# 4/3/2/1-Phase PWM Controller for AMD AM2/AM2+/AM3 CPUs

### **General Description**

The RT8868 is a 4/3/2/1-phase synchronous buck controller with two integrated MOSFET drivers for CPU power application and a single-phase buck with integrated MOSFET driver for North-Bridge (NB) chipset. The RT8868 uses differential inductor DCR current sense to achieve phase current balance and active voltage positioning. Other features include adjustable operating frequency, power good indication, external error-amp compensation, over voltage protection, over current protection and enable/shutdown for various applications. The RT8868 comes in a small footprint with WQFN-48L 7x7 package.

### **Applications**

- Desktop CPU Core Power

- Low Voltage, High Current DC/DC Converter

## **Ordering Information**

RT8868□□

└Package Type

QW: WQFN-48L 7x7 (W-Type)

-Lead Plating System

G: Green (Halogen Free and Pb Free) Z: ECO (Ecological Element with

Halogen Free and Pb free)

Note:

Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

## **Marking Information**

RT8868GQW

RT8868 GQW YMDNN RT8868GQW : Product Code

YMDNN: Date Code

RT8868ZQW

RT8868 ZQW YMDNN RT8868ZQW: Product Code

YMDNN: Date Code

#### **Features**

- 12V Power Supply Voltage

- 4/3/2/-Phase Power Conversion for V<sub>CORE</sub> Power

- 3 Embedded MOSFET Drivers (2 for CPU and 1 for NB)

- Internal Regulated 5V Output

- Support AMD AM2 6-bit Parallel and AM2+ 7-bit Serial VID Tables

- Support 3.4MHz High Speed I<sup>2</sup>C

- Continuous Differential Inductor DCR Current Sense

- Adjustable Frequency (Typically at 300kHz)

- Selectable 1 or 2 Phase in Power-Saving (PS) Mode

- Phase-Interleaving for V<sub>CORE</sub> Controller

- Power Good Indication

- Adjustable Over Current Protection

- Over Voltage Protection

- Small 48-Lead WQFN Package

- RoHS Compliant and Halogen Free

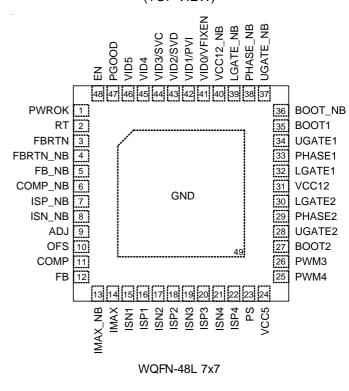

### **Pin Configurations**

(TOP VIEW)

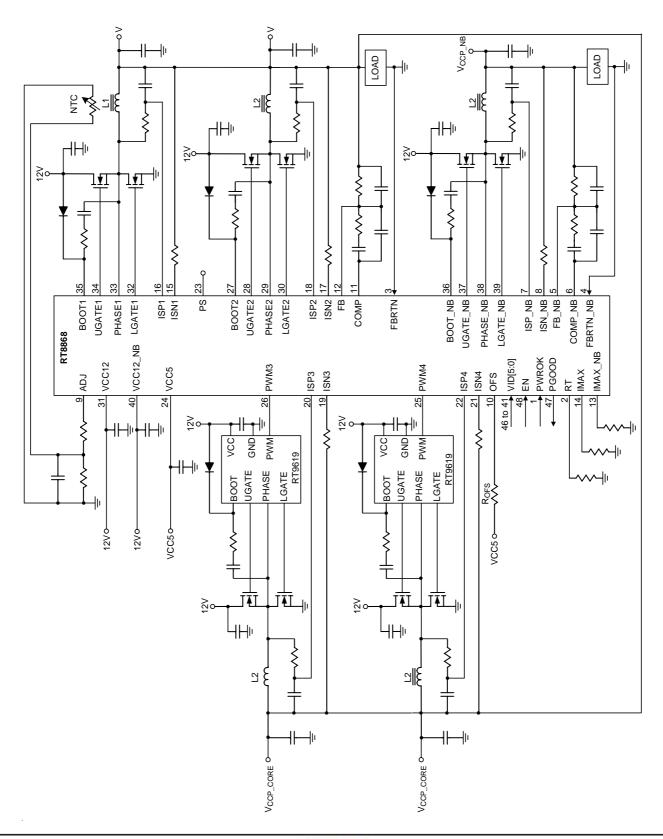

# **Typical Application Circuit**

Table 1. 7-bit VID Code Table for AM2+/AM3 CPU (Serial)

| SVID[6:0] | Voltage | SVID[6:0] | Voltage | SVID[6:0] | Voltage | SVID[6:0] | Voltage |

|-----------|---------|-----------|---------|-----------|---------|-----------|---------|

| 0000000   | 1.5500  | 0100000   | 1.1500  | 1000000   | 0.7500  | 1100000   | 0.3500  |

| 0000001   | 1.5375  | 0100001   | 1.1375  | 1000001   | 0.7375  | 1100001   | 0.3375  |

| 0000010   | 1.5250  | 0100010   | 1.1250  | 1000010   | 0.7250  | 1100010   | 0.3250  |

| 0000011   | 1.5125  | 0100011   | 1.1125  | 1000011   | 0.7125  | 1100011   | 0.3125  |

| 0000100   | 1.5000  | 0100100   | 1.1000  | 1000100   | 0.7000  | 1100100   | 0.3000  |

| 0000101   | 1.4875  | 0100101   | 1.0875  | 1000101   | 0.6875  | 1100101   | 0.2875  |

| 0000110   | 1.4750  | 0100110   | 1.0750  | 1000110   | 0.6750  | 1100110   | 0.2750  |

| 0000111   | 1.4625  | 0100111   | 1.0625  | 1000111   | 0.6625  | 1100111   | 0.2625  |

| 0001000   | 1.4500  | 0101000   | 1.0500  | 1001000   | 0.6500  | 1101000   | 0.2500  |

| 0001001   | 1.4375  | 0101001   | 1.0375  | 1001001   | 0.6375  | 1101001   | 0.2375  |

| 0001010   | 1.4250  | 0101010   | 1.0250  | 1001010   | 0.6250  | 1101010   | 0.2250  |

| 0001011   | 1.4125  | 0101011   | 1.0125  | 1001011   | 0.6125  | 1101011   | 0.2125  |

| 0001100   | 1.4000  | 0101100   | 1.0000  | 1001100   | 0.6000  | 1101100   | 0.2000  |

| 0001101   | 1.3875  | 0101101   | 0.9875  | 1001101   | 0.5875  | 1101101   | 0.1875  |

| 0001110   | 1.3750  | 0101110   | 0.9750  | 1001110   | 0.5750  | 1101110   | 0.1750  |

| 0001111   | 1.3625  | 0101111   | 0.9625  | 1001111   | 0.5625  | 1101111   | 0.1625  |

| 0010000   | 1.3500  | 0110000   | 0.9500  | 1010000   | 0.5500  | 1110000   | 0.1500  |

| 0010001   | 1.3375  | 0110001   | 0.9375  | 1010001   | 0.5375  | 1110001   | 0.1375  |

| 0010010   | 1.3250  | 0110010   | 0.9250  | 1010010   | 0.5250  | 1110010   | 0.1250  |

| 0010011   | 1.3125  | 0110011   | 0.9125  | 1010011   | 0.5125  | 1110011   | 0.1125  |

| 0010100   | 1.3000  | 0110100   | 0.9000  | 1010100   | 0.5000  | 1110100   | 0.1000  |

| 0010101   | 1.2875  | 0110101   | 0.8875  | 1010101   | 0.4875  | 1110101   | 0.0875  |

| 0010110   | 1.2750  | 0110110   | 0.8750  | 1010110   | 0.4750  | 1110110   | 0.0750  |

| 0010111   | 1.2625  | 0110111   | 0.8625  | 1010111   | 0.4625  | 1110111   | 0.0675  |

| 0011000   | 1.2500  | 0111000   | 0.8500  | 1011000   | 0.4500  | 1111000   | 0.0500  |

| 0011001   | 1.2375  | 0111001   | 0.8375  | 1011001   | 0.4375  | 1111001   | 0.0375  |

| 0011010   | 1.2250  | 0111010   | 0.8250  | 1011010   | 0.4250  | 1111010   | 0.0250  |

| 0011011   | 1.2125  | 0111011   | 0.8125  | 1011011   | 0.4125  | 1111011   | 0.0125  |

| 0011100   | 1.2000  | 0111100   | 0.8000  | 1011100   | 0.4000  | 1111100   | OFF     |

| 0011101   | 1.1875  | 0111101   | 0.7875  | 1011101   | 0.3875  | 1111101   | OFF     |

| 0011110   | 1.1750  | 0111110   | 0.7750  | 1011110   | 0.3750  | 1111110   | OFF     |

| 0011111   | 1.1625  | 0111111   | 0.7625  | 1011111   | 0.3625  | 1111111   | OFF     |

Table 2. 6-bit VID Code Table for AM2 CPU (Parallel)

| VID[5:0] | Voltage | VID[5:0] | Voltage | VID[5:0] | Voltage | VID[5:0] | Voltage |

|----------|---------|----------|---------|----------|---------|----------|---------|

| 000000   | 1.5500  | 010000   | 1.1500  | 100000   | 0.7625  | 110000   | 0.5625  |

| 000001   | 1.5250  | 010001   | 1.1250  | 100001   | 0.7500  | 110001   | 0.5500  |

| 000010   | 1.5000  | 010010   | 1.1000  | 100010   | 0.7375  | 110010   | 0.5375  |

| 000011   | 1.4750  | 010011   | 1.0750  | 100011   | 0.7250  | 110011   | 0.5250  |

| 000100   | 1.4500  | 010100   | 1.0500  | 100100   | 0.7125  | 110100   | 0.5125  |

| 000101   | 1.4250  | 010101   | 1.0250  | 100101   | 0.7000  | 110101   | 0.5000  |

| 000110   | 1.4000  | 010110   | 1.0000  | 100110   | 0.6875  | 110110   | 0.4875  |

| 000111   | 1.3750  | 010111   | 0.9750  | 100111   | 0.6750  | 110111   | 0.4750  |

| 001000   | 1.3500  | 011000   | 0.9500  | 101000   | 0.6625  | 111000   | 0.4625  |

| 001001   | 1.3250  | 011001   | 0.9250  | 101001   | 0.6500  | 111001   | 0.4500  |

| 001010   | 1.3000  | 011010   | 0.9000  | 101010   | 0.6375  | 111010   | 0.4375  |

| 001011   | 1.2750  | 011011   | 0.8750  | 101011   | 0.6250  | 111011   | 0.4250  |

| 001100   | 1.2500  | 011100   | 0.8500  | 101100   | 0.6125  | 111100   | 0.4125  |

| 001101   | 1.2250  | 011101   | 0.8250  | 101101   | 0.6000  | 111101   | 0.4000  |

| 001110   | 1.2000  | 011110   | 0.8000  | 101110   | 0.5875  | 111110   | 0.3875  |

| 001111   | 1.1750  | 011111   | 0.7750  | 101111   | 0.5750  | 111111   | 0.3750  |

# **Functional Pin Description**

| Pin No.               | Pin Name                 | Pin Function                                                                                                                             |  |  |  |

|-----------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1                     | PWROK                    | PWROK Input Signal.                                                                                                                      |  |  |  |

| 2                     | RT                       | Connect this Pin to GND by a Resistor to Adjust Frequency.                                                                               |  |  |  |

| 3                     | FBRTN                    | Remote Sense Ground for CORE.                                                                                                            |  |  |  |

| 4 FBRTN_NB            |                          | Remote Sense Ground for NB.                                                                                                              |  |  |  |

| 4 FBRIN_NB<br>5 FB_NB |                          | Inverting Input of Error-Amp for NB.                                                                                                     |  |  |  |

| 6                     | COMP_NB                  | Output of Error-Amp and Input of PWM Comparator for NB.                                                                                  |  |  |  |

| 7                     | ISP_NB                   | Positive Current Sense Pin of NB.                                                                                                        |  |  |  |

| 8                     | ISN_NB                   | Negative Current Sense Pin of NB.                                                                                                        |  |  |  |

| 9                     | ADJ                      | Connect this Pin to GND by a Resistor to set Load Line of VCORE.                                                                         |  |  |  |

| 10                    | OFS                      | Connect this Pin to 5VCC by a Resistor to set No-Load Offset Voltage of $V_{\mbox{\footnotesize{CORE}}}.$                                |  |  |  |

| 11                    | COMP                     | Output of Error-Amp and Input of PWM Comparator of $V_{\mbox{CORE}}$ .                                                                   |  |  |  |

| 12                    | FB                       | Inverting Input of Error-Amp of V <sub>CORE</sub> .                                                                                      |  |  |  |

| 13                    | IMAX_NB                  | Connect this Pin to GND by a Resistor to set OCP of NB.                                                                                  |  |  |  |

| 14                    | IMAX                     | Connect this Pin to GND by a Resistor to set OCP of VCORE.                                                                               |  |  |  |

| 15, 17, 19, 21        | ISN1, ISN2, ISN3, ISN4   | Negative Current Sense Pin of Channel 1, 2, 3 and 4.                                                                                     |  |  |  |

| 16, 18, 20, 22        | ISP1, ISP2, ISP3, ISP4   | Positive Current Sense Pin of Channel 1, 2, 3 and 4.                                                                                     |  |  |  |

| 23                    | PS                       | Power Saving Mode Selection Pin.                                                                                                         |  |  |  |

| 24                    | VCC5                     | Output of Internal 5V Regulator for Control Circuits Power Supply. Connect this Pin to GND by a Ceramic Capacitor Larger than $1\mu F$ . |  |  |  |

| 25,26                 | PWM4, PWM3               | PWM Output for Channel 4 and Channel 3.                                                                                                  |  |  |  |

| 27, 35, 36            | BOOT2, BOOT1, BOOT_NB    | Bootstrap Supply for Channel 2 and Channel 1 and NB.                                                                                     |  |  |  |

| 28, 34, 37            | UGATE2, UGATE1, UGATE_NB | Upper Gate Driver for Channel 2 and Channel 1 and NB.                                                                                    |  |  |  |

| 29, 33, 38            | PHASE2, PHASE1, PHASE_NB | Switching Node of Channel 2 and Channel 1 and NB.                                                                                        |  |  |  |

| 30, 32, 39            | LGATE2, LGATE1, LGATE_NB | Lower Gate Driver for Channel 2 and Channel 1 and NB.                                                                                    |  |  |  |

| 31, 40                | VCC12, VCC12_NB          | IC Power Supply. Connect this pin to 12V.                                                                                                |  |  |  |

| 41                    | VID0/VFIXEN              | PVI Mode: Used as Voltage Identification Input for DAC. SVI Mode: Functions as VFIXEN Selection Input.                                   |  |  |  |

| 42                    | VID1/PVI                 | This Pin Selects PVI/SVI Mode Based on the State of this Pin Prior to EN Signal. PVI Mode: Used as Voltage Identification Input for DAC. |  |  |  |

| 43                    | VID2/SVD                 | PVI Mode: Used as Voltage Identification Input for DAC. SVI Mode: Serial Data Input.                                                     |  |  |  |

| 44                    | VID3/SVC                 | PVI Mode: Used as Voltage Identification Input for DAC. SVI Mode: Serial Clock Input.                                                    |  |  |  |

| 45, 46                | VID4, VID5               | PVI Mode: Used as Voltage Identification Input for DAC.                                                                                  |  |  |  |

| 47                    | PGOOD                    | Power Good Indicator (open drain).                                                                                                       |  |  |  |

| 48                    | EN                       | Enable Input Signal.                                                                                                                     |  |  |  |

| 49<br>(Exposed pad)   | GND                      | Reference Ground for the IC. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.         |  |  |  |

Copyright ©2014 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

DS8868-05 January 2014 www.richtek.com

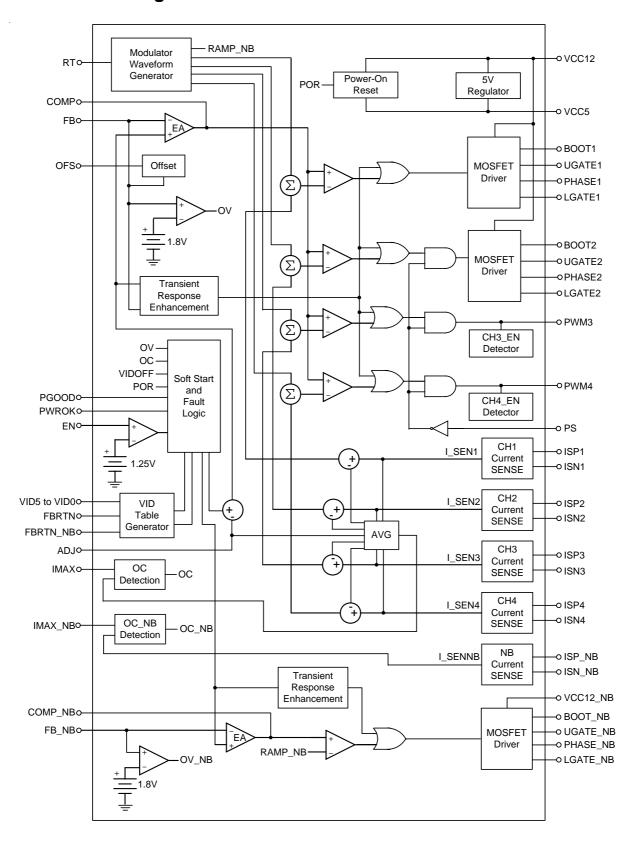

# **Function Block Diagram**

### **Absolute Maximum Ratings** (Note 1)

| Supply Input Voltage                                                        |                                                       |

|-----------------------------------------------------------------------------|-------------------------------------------------------|

| • BOOTx to PHASEx                                                           |                                                       |

| PHASEx to GND                                                               |                                                       |

| DC                                                                          |                                                       |

| <20ns                                                                       |                                                       |

| UGATEx to GND                                                               |                                                       |

| DC                                                                          | $(V_{PHASE} - 0.3V)$ to $(V_{BOOT} + 0.3V)$           |

| <20ns                                                                       | (V <sub>PHASE</sub> – 5V) to (V <sub>BOOT</sub> + 5V) |

| LGATEx to GND                                                               |                                                       |

| DC                                                                          | (GND – 0.3V) to (V <sub>CC</sub> + 0.3V)              |

| <20ns                                                                       | (GND – 5V) to (V <sub>CC</sub> + 5V)                  |

| Input/Output Voltage or I/O Voltage                                         |                                                       |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                                                       |

| WQFN-48L 7x7                                                                | 3.226W                                                |

| Package Thermal Resistance (Note 2)                                         |                                                       |

| WQFN-48L 7x7, $\theta_{JA}$                                                 | 31°C/W                                                |

| WQFN-48L 7x7, $\theta_{JC}$                                                 | 6°C/W                                                 |

| Junction Temperature                                                        | 150°C                                                 |

| • Lead Temperature (Soldering, 10 sec.)                                     | 260°C                                                 |

| Storage Temperature Range                                                   |                                                       |

| ESD Susceptibility (Note 3)                                                 |                                                       |

| HBM (Human Body Model)                                                      | 2kV                                                   |

|                                                                             |                                                       |

### Recommended Operating Conditions (Note 4)

### **Electrical Characteristics**

( $V_{VCC12}$  = 12V, GND = 0V,  $T_A$  = 25°C, unless otherwise specified)

| Parameter               | Symbol                | Test Conditions          | Min  | Тур | Max  | Unit |

|-------------------------|-----------------------|--------------------------|------|-----|------|------|

| VCC Supply Input        |                       |                          |      |     |      |      |

| VCC12 Supply Voltage    | V <sub>VCC12</sub>    |                          | 10.8 | 12  | 13.2 | V    |

| VCC12 Supply Current    | I <sub>VCC12</sub>    |                          |      | 10  |      | mA   |

| VCC12_NB Supply Voltage | V <sub>VCC12_NB</sub> |                          | 10.8 | 12  | 13.2 | ٧    |

| VCC12_NB Supply Current | I <sub>VCC12_NB</sub> |                          |      | 5   |      | mA   |

| VCC5 Power              |                       |                          |      |     |      |      |

| VCC5 Supply Voltage     | V <sub>VCC5</sub>     | I <sub>LOAD</sub> = 10mA | 4.9  | 5   | 5.1  | V    |

| VCC5 Output Sourcing    | I <sub>VCC5</sub>     |                          | 10   |     |      | mA   |

| Power On Reset          |                       |                          |      |     |      |      |

| VCC12 Rising Threshold  | V <sub>VCC12TH</sub>  | VCC12 Rising             | 9.4  | 9.8 | 10.2 | V    |

| VCC12 Hysteresis        | V <sub>VCC12HY</sub>  | VCC12 Falling            |      | 0.9 |      | V    |

Copyright ©2014 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS8868-05 January 2014

| Parameter                        |             | Symbol                    | Test Conditions                                  | Min                        | Тур                        | Max                        | Unit  |

|----------------------------------|-------------|---------------------------|--------------------------------------------------|----------------------------|----------------------------|----------------------------|-------|

| Input Threshold                  |             |                           |                                                  |                            |                            |                            |       |

| Enable Input                     | Logic-High  | V <sub>ENHI</sub>         | EN Rising                                        | 2                          |                            |                            | V     |

| Threshold Voltage                | Logic-Low   | V <sub>ENLO</sub>         | EN Falling                                       |                            |                            | 8.0                        | V     |

| PWROK Input                      | Logic-High  | V <sub>POKHI</sub>        | PWROK Rising                                     | 2                          |                            |                            | V     |

| Threshold Voltage                | Logic-Low   | V <sub>POKLO</sub>        | PWROK Falling                                    |                            |                            | 0.8                        | -     |

| VID5 to VID0 Rising              | g Threshold | V <sub>VID5 to 0</sub>    | VID5 to VID0 Rising                              | 0.75                       | 0.8                        | 0.85                       | V     |

| VID5 to VID0 Hyste               |             | V VID5 to 0 HYS           | VID5 to VID0 Falling                             |                            | 25                         |                            | mV    |

| VID5 to VID0 Pull-E<br>Current   | Down        | I <sub>VID5 to 0</sub>    | V <sub>VID5 to 0</sub> = 1.5V                    |                            | 16                         | 30                         | μΑ    |

| Reference Voltage                | Accuracy    | _                         |                                                  | i                          |                            |                            |       |

|                                  |             |                           | 1V to 1.55V                                      | -0.5                       |                            | 0.5                        | %     |

| DAC Accuracy                     |             |                           | 0.8V to 1V                                       | -8                         |                            | 8                          | mV    |

|                                  |             |                           | 0.5V to 0.8V                                     | -10                        |                            | 10                         | mV    |

| Error Amplifier                  |             |                           |                                                  |                            |                            |                            |       |

| DC Gain                          |             | A <sub>DC</sub>           | No Load                                          |                            | 80                         |                            | dB    |

| Gain-Bandwidth                   |             | GBW                       | C <sub>LOAD</sub> = 10pF                         |                            | 10                         |                            | MHz   |

| Slew Rate                        |             | SR                        | C <sub>LOAD</sub> = 10pF                         | 10                         |                            |                            | V/μs  |

| Output Voltage Rar               | nge         | V <sub>COMP</sub>         | $R_{LOAD} = 47k\Omega$                           | 0.5                        |                            | 3.6                        | V     |

| Power Good                       |             |                           |                                                  |                            |                            |                            |       |

| Over Voltage Thres               | shold       | V <sub>PGOOD-OV</sub>     | FB Rising                                        | V <sub>DAC</sub><br>+210mV | V <sub>DAC</sub><br>+240mV | V <sub>DAC</sub><br>+270mV | V     |

| Under Voltage Thre               | eshold      | V <sub>PGOOD-UV</sub>     | FB Falling                                       | V <sub>DAC</sub>           | V <sub>DAC</sub><br>-300mV | V <sub>DAC</sub><br>-270mV | V     |

| Over Voltage Thres               | shold_NB    | V <sub>P</sub> GOOD-OV_NB | FB_NB Rising                                     | V <sub>DAC</sub><br>+210mV | V <sub>DAC</sub><br>+240mV | V <sub>DAC</sub><br>+270mV | ٧     |

| Under Voltage Thre               | eshold_NB   | V <sub>PGOOD-UV_NB</sub>  | FB_NB Falling                                    | V <sub>DAC</sub><br>-330mV | V <sub>DAC</sub><br>-300mV | V <sub>DAC</sub><br>-270mV | V     |

| Power Good Low V                 | /oltage     | V <sub>PGOOD</sub>        | I <sub>PGOOD</sub> = 4mA                         |                            |                            | 0.4                        | V     |

| Current Sense Am                 | plifier     |                           |                                                  |                            |                            |                            |       |

| Max Current                      |             | I <sub>GMMA</sub> X       | V <sub>CSP</sub> = 1.3V<br>Sink Current from CSN | 100                        |                            |                            | μΑ    |

| Input Offset Voltage             | Э           | Voscs                     |                                                  | -2                         | 0                          | 2                          | mV    |

| Oscillator                       |             |                           |                                                  |                            |                            |                            |       |

| Running Frequency                | /           | fosc                      | $R_{RT} = 40k\Omega$                             | 270                        | 300                        | 330                        | kHz   |

| Ramp Amplitude V <sub>RAMP</sub> |             |                           |                                                  |                            | 1.6                        |                            | V     |

| Soft-Start                       |             | •                         | •                                                |                            |                            |                            |       |

| Soft-Start Slew Rat              | <br>е       | SR <sub>SS</sub>          | Slew Rate                                        | 2.5                        | 3.25                       | 4                          | mV/μs |

| VID change Slew F                |             | SR <sub>VID</sub>         | Slew Rate                                        | 2.5                        | 3.25                       | 4                          | mV/μs |

| 3                                |             | 1 115                     |                                                  | 1                          |                            |                            |       |

| Parameter              | Symbol               | Test Conditions                                                     | Min  | Тур | Max   | Unit |

|------------------------|----------------------|---------------------------------------------------------------------|------|-----|-------|------|

| Protection             |                      |                                                                     |      |     |       |      |

| Over Veltage Threehold | V <sub>OVP</sub>     | Sweep FB Voltage                                                    | 1.7  | 1.8 | 1.9   | V    |

| Over Voltage Threshold | V <sub>OVP_NB</sub>  | Sweep FB_NB Voltage                                                 | 1.7  | 1.8 | 1.9   | V    |

|                        | I <sub>OCP</sub>     | $R_{IMAX} = 40k\Omega$                                              | 64.5 | 83  | 101.5 | μΑ   |

| Over Over the state    | $V_{IMAX}$           | $R_{IMAX} = 40k\Omega$                                              | 1.44 | 1.6 | 1.76  | V    |

| Over-Current Threshold | I <sub>OCP_NB</sub>  | $R_{IMAX\_NB} = 40k\Omega$                                          | 64.5 | 83  | 101.5 | μΑ   |

|                        | V <sub>IMAX_NB</sub> | $R_{IMAX\_NB} = 40k\Omega$                                          | 1.44 | 1.6 | 1.76  | V    |

| Gate Driver            | •                    |                                                                     | •    |     |       |      |

| UGATE Drive Source     | RUGATEsr             | V <sub>BOOT</sub> – V <sub>PHASE</sub> = 8V<br>250mA Source Current |      | 1   |       | Ω    |

| UGATE Drive Sink       | R <sub>UGATEsk</sub> | VBOOT – VPHASE = 8V<br>250mA Sink Current                           |      | 1   |       | Ω    |

| LGATE Drive Source     | R <sub>LGATEsr</sub> | V <sub>LGATE</sub> = 8V                                             |      | 1   |       | Ω    |

| LGATE Drive Sink       | R <sub>LGATEsk</sub> | 250mA Sink Current                                                  |      | 0.9 |       | Ω    |

- **Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity four-layer test board per JEDEC 51-7.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

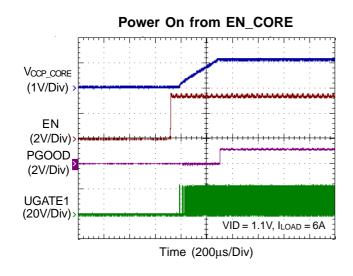

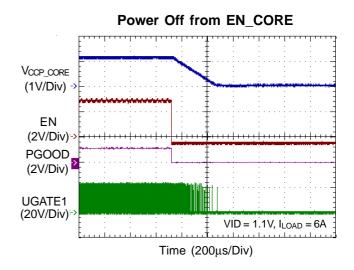

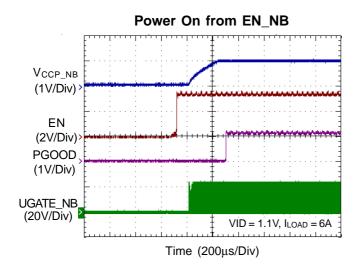

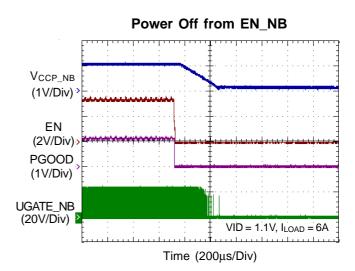

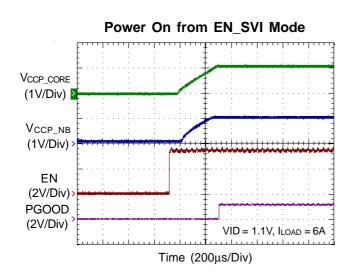

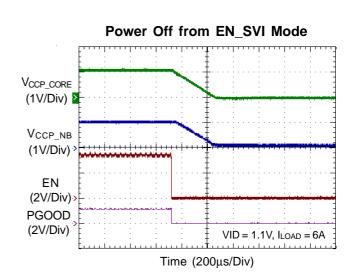

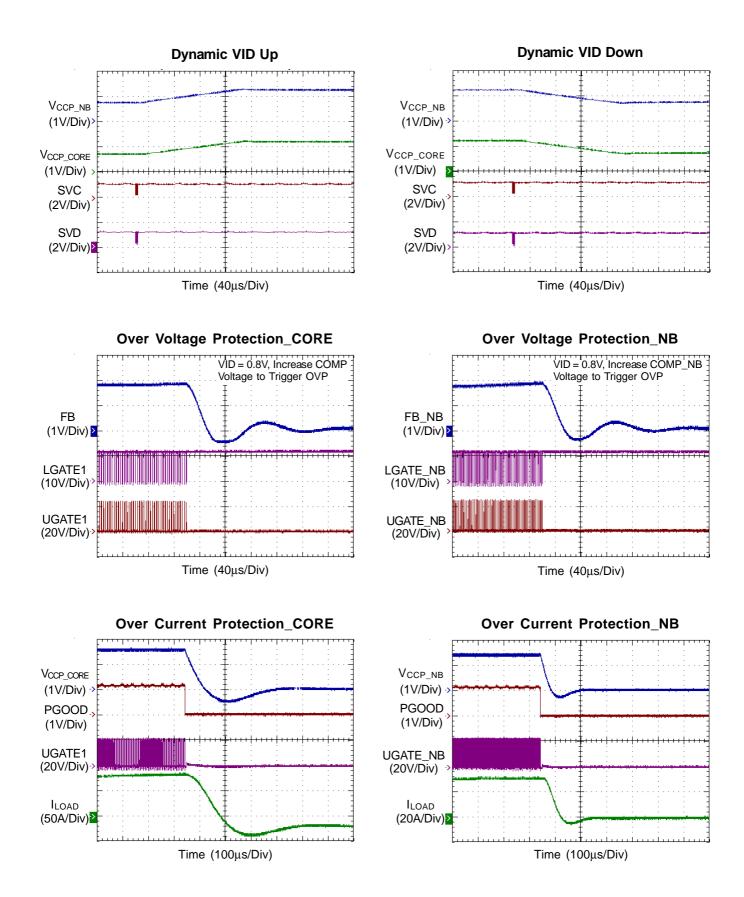

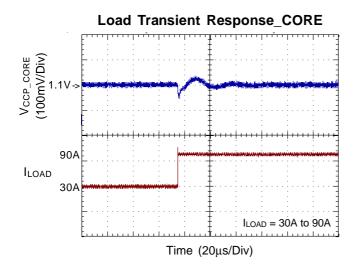

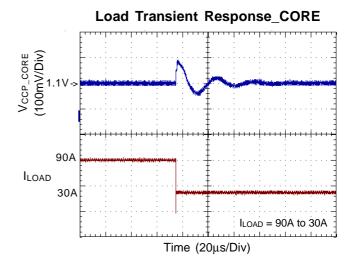

# **Typical Operating Characteristics**

Copyright ©2014 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS8868-05 January 2014 www.richtek.com

### **Application Information**

The RT8868 is a dual output PWM controller that supports hybrid power control of AMD processors which operate from either a 6-bit Parallel VID Interface (PVI) or a Serial VID Interface (SVI). One of the outputs is a 4/3/2/1-phase PWM controller with two integrated MOSFET drivers to support CPU core voltage (VDD) and another is a singlephase buck controller with an integrated MOSFET driver to power North-Bridge (NB) chipset (VDDNB) in SVI mode. In PVI mode, only multiphase PWM controller is active for single plane VDD only processor.

Richtek's proprietary Burst Transient Response(BTR<sup>TM</sup>) provides fast initial response to high di/dt load transients and requires less bulk and ceramic output capacitance to meet transient regulation specifications. The RT8868 incorporates differential voltage sensing, continuous inductor DCR phase current sensing, programmable loadline voltage positioning and offset voltage to provide high accuracy regulated power for both VDD and VDDNB. While VDDNB is enabled in SVI mode, it will be automatically phase-shifted with respect to the CPU Core phases in order to reduce the total input RMS current amount.

#### CPU\_TYPE Detection and System Start-Up

At system start-up, on the rising-edge of EN signal, the RT8868 monitors the status of VID1 and latches the PVI mode (VID1 = 1) or SVI mode (VID1 = 0).

#### **PVI Mode**

PVI is a 6-bit-wide parallel interface used to address the CPU Core section reference. According to the selected code, the device sets the Core section reference and regulates its output voltage according to Table 2. In this mode, NB section is kept in high impedance. Furthermore, PWROK information is ignored as well since the signal only applies to the SVI protocol.

#### **SVI Mode**

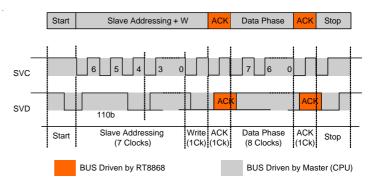

SVI is a two wire, Clock and Data, bus that connects a single master (CPU) to one slave (RT8868). The master initiates and terminates SVI transactions and drives the clock, SVC, and the data, SVD, during a transaction. The slave receives the SVI transactions and acts accordingly. SVI wire protocol is based on fast-mode I<sup>2</sup>C as shown in Figure 1. SVI interface also considers two additional signals needed to manage the system start-up. These signals are EN and PWROK. The device asserts a PGOOD signal if the output voltages are in regulation.

Figure 1. SVI Communication-Send Byte

#### **Set VID Command**

The Set VID Command is defined as the command sequence that the CPU issues on the SVI bus to modify the voltage level of the Core section and NB section, as shown is Figure 1. During a Set VID Command, the processor sends the start (Start) sequence followed by the address of the Section which the Set VID Command applies. The processor then sends the write (WRITE) bit. After the write bit, the Voltage Regulator (VR) sends the acknowledge (ACK) bit. The processor then sends the VID bits code during the data phase. The VR sends the acknowledge (ACK) bit after the data phase. Finally, the processor sends the stop (Stop) sequence. After the VR has detected the stop, it performs an On-the-Fly VID transition for the addressed section(s). Refer to Table 3 for the details of SVI send byte.

The RT8868 is able to manage individual power off for both VCORE and NB sections. The CPU may issue a serial VID command to power off or power on one section while the other one remains powered. In this case, the PGOOD signal remains asserted.

Table 3. SVI Send Byte-Address and Data Phase Description / Example

| 2000ptio, =xap.0 |                                                  |  |  |  |  |  |  |

|------------------|--------------------------------------------------|--|--|--|--|--|--|

| bits             | Description                                      |  |  |  |  |  |  |

|                  | Address Phase                                    |  |  |  |  |  |  |

| 6:4              | Always 110b                                      |  |  |  |  |  |  |

| 3                | Not Applicable, ignored.                         |  |  |  |  |  |  |

| 2                | Not Applicable, ignored.                         |  |  |  |  |  |  |

|                  | CORE Section. (Note)                             |  |  |  |  |  |  |

| 1                | If set then the following data byte contains the |  |  |  |  |  |  |

|                  | VID code for CORE Section.                       |  |  |  |  |  |  |

|                  | NB Section. (Note)                               |  |  |  |  |  |  |

| 0                | If set then the following data byte contains the |  |  |  |  |  |  |

|                  | VID code for NB Section.                         |  |  |  |  |  |  |

| Data Phase       |                                                  |  |  |  |  |  |  |

| 7                | PSI_L Flag (Active Low). When asserted, the      |  |  |  |  |  |  |

| /                | VR is allowed to enter Power-Saving Mode.        |  |  |  |  |  |  |

| 6:0              | VID Code.                                        |  |  |  |  |  |  |

Note: Assertion in both bit 1 and 0 will address the VID code to both CORE and NB simultaneously.

#### Example:

| SVI Address<br>Bits [6 : 0] | Description                        |  |  |  |  |

|-----------------------------|------------------------------------|--|--|--|--|

| 1100_000                    | Should be ignored.                 |  |  |  |  |

| 1100_001                    | Set VID on VDDNB.                  |  |  |  |  |

| 1100_110                    | Set VID on VDD0 and VDD1.          |  |  |  |  |

| 1100_100                    | Set VID on VDD1.                   |  |  |  |  |

| 1100_010                    | Set VID on VDD0 or VDD (Uniplane). |  |  |  |  |

| 1100_111                    | Set VID on VDDNB, VDD0 and VDD1.   |  |  |  |  |

#### **PWROK De-assertion**

PWROK stays low after EN signal is asserted, and the controller regulates all the planes according to the Pre-PWROK Metal VID.

PGOOD is de-asserted as long as Pre-PWROK Metal VID voltage is out of the initial voltage specifications.

#### **V\_FIX Mode Function**

Anytime the pin VID0/VFIXEN is pulled high, the controller enters V-FIX mode. When in V\_FIX mode, both VCORE and NB section voltages are governed by the information shown in Table 4. Regardless of the state of PWROK, the device will work in SVI mode. SVC and SVD are considered as static VID and the output voltage will be changed according to their status. Dynamic SVC/SVD-change management is provided in this condition. V\_FIX mode is intended for system debug only.

Table 4. V\_FIX Mode and Pre-PWROK Metal VID

|     |     | Output Voltage (V)     |            |  |  |

|-----|-----|------------------------|------------|--|--|

| SVC | SVD | Pre-PWROK<br>Metal VID | V_FIX Mode |  |  |

| 0   | 0   | 1.1V                   | 1.4V       |  |  |

| 0   | 1   | 1.0V                   | 1.2V       |  |  |

| 1   | 0   | 0.9V                   | 1.0V       |  |  |

| 1   | 1   | 0.8V                   | 0.8V       |  |  |

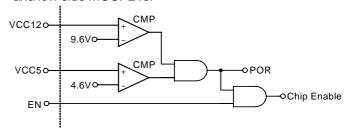

#### **Power Ready Detection**

During start-up, the RT8868 will detect VCC12, VCC5 and EN signal. Figure 2 shows the power ready detection circuit. When VCC12 > 9.6V and VCC5 > 4.6V, POR (Power On Reset) will go high. POR is the internal signal to indicate all input powers are ready to allow the RT8868 and the companioned MOSFET drivers to work properly. When POR = L, the RT8868 will turn off both high side and low side MOSFETs.

Figure 2. Circuit for Power Ready Detection

#### **Power-Up Sequencing**

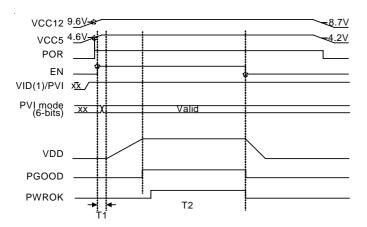

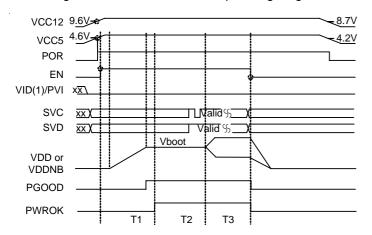

Figure 3 and 4 are the power-up sequencing diagram of the RT8868. Once power on reset is valid (POR = H), on the rising edge of the EN signal, the RT8868 detects the VID1 pin and determines whether to operate in SVI or PVI mode. Figure 3 shows the PVI-mode power sequence, the controller stays in T1 state waiting for valid parallel VID code sent by CPU. After receiving valid parallel VID code, VCORE continues ramping up to the specified voltage according to the VID code in T2 state. Figure 4 shows the SVI-mode power sequence, the controller samples the two serial VID pins, SVC and SVD. Then, the controller stores this value as the boot VID that is the so-called "Pre-PWROK Metal VID" in T1 state. After the processor starts with boot VID voltages, PWROK is asserted and the processor initializes the serial VID interface in T2 state. The processor uses the serial VID interface to issue VID commands to move the power planes from the boot VID values to the dual power planes in T3 state.

**RICHTEK** is a registered trademark of Richtek Technology Corporation.

Figure 3. PVI-Mode Power-sequencing Diagram

Figure 4. SVI-Mode Power-sequencing Diagram

#### **CORE Section Output Current Sensing**

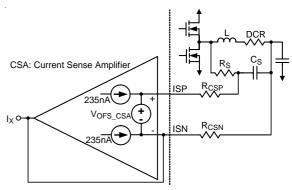

The RT8868 provides a low input offset Current Sense Amplifier (CSA) to monitor the continuous output current of each phase for  $V_{CORE}$ . Output current of CSA ( $I_X[n]$ ) is used for current balance and active voltage position as shown in Figure 5. In this inductor current sensing topology,  $R_S$  and  $C_S$  must be set according to the equation below :

$$\frac{L}{DCR} = R_S \times C_S$$

Then the output current of CSA will follow the equation below:

$$I_{X} = \frac{[I_{L} \times DCR - V_{OFS-CSA} + 235nA \times (R_{CSP} - R_{CSN})]}{R_{CSN}}$$

235nA is the typical value of the CSA input offset current.  $V_{OFS\text{-}CSA} \text{ is the input offset. Usually, } "V_{OFS\text{-}CSA} + 235nAx \\ (R_{CSP} - R_{CSN})" \text{ is negligible except at very light load and the equation can be simplified as the equation below :}$

$$I_{X} = \frac{I_{L} \times DCR}{R_{CSN}}$$

Figure 5. Current Sensing Circuit

#### **CORE Section Phase Detection**

The number of the operational phases is determined by the internal circuitry that monitors the ISNx voltages during start up. Normally, the RT8868 operates as a 4-phase PWM controller. Pull ISN4 and ISP4 to 5VCC programs 3-phase operation, pull ISN3 and ISP3 to 5VCC programs 2-phase operation, and pull ISN2 and ISP2 to 5VCC programs 1-phase operation. The RT8868 detects the voltage of ISN4, ISN3 and ISN2 at rising edge of POR. At the rising edge, the RT8868 detects whether the voltage of ISN4, ISN3 and ISN2 are higher than "VCC5-1V" respectively to decide how many phases should be active. Phase detection is only active during start up. Once POR = high, the number of operational phases is determined and latched.

#### **CORE Section Switching Frequency**

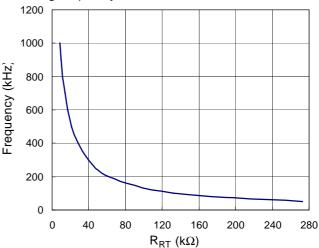

Connecting a resistor ( $R_{RT}$ ) from the RT pin to GND programs the switching frequency of each phase. Figure 6 shows the relationship between the resistance and switching frequency.

Figure 6. R<sub>RT</sub> vs. Phase switching Frequency

Copyright ©2014 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation.

DS8868-05 January 2014

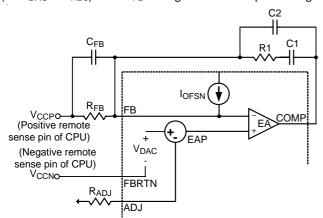

#### **CORE Section Differential Output Voltage Sensing**

The RT8868 uses differential voltage sensing by a high gain low offset error-amp as shown in Figure 7. Connect the negative on-die CPU remote sense pin to FBRTN. Connect the positive on-die remote sense pin to FB with a resistor ( $R_{FB}$ ) The error-amp compares EAP (=  $V_{DAC} - V_{ADJ}$ ) with  $V_{FB}$  to regulate the output voltage.

Figure 7. Circuit for VCORE Differential Sensing and No Load Offest

#### **CORE Section No-Load Offset**

In Figure 7,  $I_{OFSN}$  is used to generate no-load offset. Connect a resistor from OFS pin to VCC5 to activate  $I_{OFSP}$ .  $I_{OFSP}$  flows through  $R_{FB}$  from VCCP to FB pin. In this case, positive no-load offset voltage ( $V_{OFSP}$ ) is generated.

Besides I<sub>OFSP</sub>, the RT8868 generates another DC current for initial no-load negative offset. A DC current source will continuously inject typical  $9\mu A$  current into the resistors connected to ADJ pin, Therefore, the effect of this  $9\mu A$  current source and ADJ resistors should be included in the calculation of no-load offset :

$$V_{OFSP} = I_{OFSP} \times R_{FB} - 9\mu \times R_{ADJ}$$

$$= 0.4 \times \frac{R_{FB}}{R_{OFS}} - 9\mu \times R_{ADJ}$$

#### **CORE Section Programmable Load-line**

Output current of CSA is summed and averaged in the RT8868. Then  $0.5\Sigma$  ( $I_X[n]$ ) is sent to ADJ pin. Because  $\Sigma$   $I_X[n]$  is a PTC (Positive Temperature Coefficient) current, an NTC (Negative Temperature Coefficient) resistor is needed to connect ADJ pin to GND. If the NTC resistor is properly selected to compensate the temperature coefficient of  $I_X[n]$ , the voltage on ADJ pin will be

proportional to  $I_{OUT}$  without temperature effect. In the RT8868, the positive input of error-amp is " $V_{DAC} - V_{ADJ}$ ".  $V_{OUT}$  will follow " $V_{DAC} - V_{ADJ}$ ", too. Thus, the output voltage which decreases linearly with  $I_{OUT}$  is obtained. The loadline is defined as :

$$LL(loadline) = \frac{\Delta V_{OUT}}{\Delta l_{OUT}} = \frac{\Delta V_{ADJ}}{\Delta l_{OUT}} = \frac{1}{2} \times DCR \times \frac{R_{ADJ}}{R_{CSN}}$$

Briefly, the resistance of  $R_{ADJ}$  sets the resistance of loadline. The temperature coefficient of  $R_{ADJ}$  compensates the temperature effect of loadline.

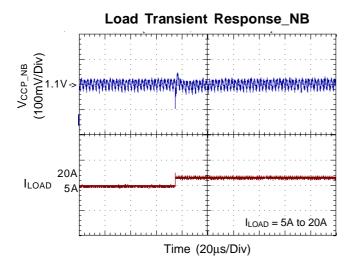

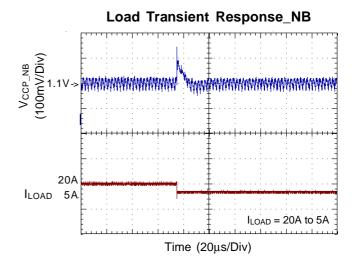

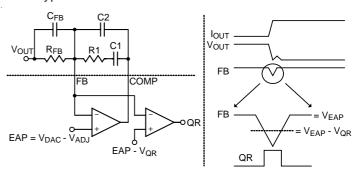

#### **CORE Section Load Transient Quick Response**

In steady state, the value of V<sub>FB</sub> is controlled to be very close to V<sub>EAP</sub>. However, a load step transient from light load to heavy load can still cause V<sub>FB</sub> to become lower than V<sub>EAP</sub> by several tens of mV. In prior design, owing to limited control bandwidth, it is difficult for the controller to prevent V<sub>OUT</sub> undershoot during quick load transient from light load to heavy load. The RT8868 has a built-in proprietary Burst Transient Response (BTR<sup>TM</sup>) technology that detects load transient by comparing VFB and VEAP. If  $V_{FB}$  suddenly drops below " $V_{EAP} - V_{QR}$ " ( $V_{QR}$  is a predetermined voltage), the quick response indicator QR rises up. When QR = high, the RT8868 turns on all high side MOSFETs and turns off all low side MOSFETs. The sensitivity of quick response can be adjusted by the values of CFB and RFB. Smaller RFB and/or larger CFB will make QR easier to be triggered. Figure 8 illustrates the circuit and typical waveforms.

Figure 8. Load Transient Quick Response

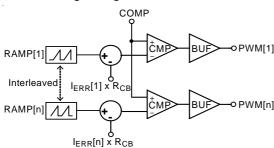

#### **CORE Section Current Balance**

In Figure 9,  $I_X[n]$  is the current signal which is proportional to the current flowing through channel n. The current error signals  $I_{ERR}[n]$  (=  $I_X[n]$  – AVG( $I_X[n]$ )) are used to raise or lower the valley of internal sawtooth waveforms (EAMP[1]

to RAMP[n]) which is compared with error-amp output (COMP) to generate PWM signal. Raising the valley of sawtooth waveform will decrease the PWM duty of the corresponding channel, while lowering the sawtooth waveform valley will increase the PWM duty. Eventually, the current flowing through each channel will be balanced.

Figure 9. Circuit Channel Current Balance

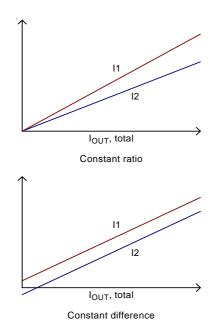

#### **CORE Section Phase Current Adjustment**

If phase current is not balanced due to asymmetric PCB layout of power stage, external resistors can be adjusted to correct current imbalance. Figure 10 shows two types of current imbalance, constant ratio type and constant difference type. If the initial current distribution is constant ratio type, according to Equation (3), reducing  $R_{CSN}[1]$  can reduce  $I_L[1]$  and improve current balance. If the initial current distribution is constant difference type, according to Equation (2), increasing  $R_{CSP}[1]$  can reduce  $I_L[1]$  and improve current balance.

Figure 10. Category of Phase Current Imbalance

#### **CORE Section Over Current Protection (OCP)**

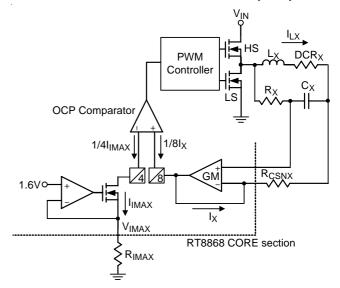

Figure 11. Over Current Protection for CORE Section

CORE section uses an external resistor  $R_{IMAX}$  connected to IMAX pin to generate a reference current  $I_{MAX}$  for over current protection as depicted in Figure 11.

$$I_{IMAX} = \frac{V_{IMAX}}{R_{IMAX}}$$

where  $V_{IMAX}$  is typically 1.6V. The RT8868 senses each phase current  $I_X$  and the OCP comparator compares sensed average current with the reference current. Equivalently, the maximum phase average current  $I_{LX(MAX)}$  is calculated as below :

$$\begin{split} &\frac{1}{4} \times I_{IMAX} = \frac{1}{8} \times I_{X(MAX)} \\ &I_{X(MAX)} = 2 \times I_{IMAX} = 2 \times \frac{V_{IMAX}}{R_{IMAX}} \\ &I_{LX(MAX)} = I_{X(MAX)} \times \frac{R_{CSNX}}{DCR_X} = 2 \times \frac{V_{IMAX}}{R_{IMAX}} \times \frac{R_{CSNX}}{DCR_X} \end{split}$$

Once  $I_X$  is larger than 2 x  $I_{IMAX}$ , the OCP of CORE section is triggered and latched. Then, the RT8868 will turn off both high side MOSFET and low side MOSFET of all channels. A 100 $\mu$ s delay is used in OCP detection circuit to prevent false trigger.

Except the normal OCP function described above, there is another short circuit OCP function especially designed for short circuit protection. Since short circuit may cause catastrophic damage over a very short period, the short circuit OCP should have a very short delay for triggering OCP latch. Also to prevent false trigger, the trigger level

d. RICHTEK is a registered trademark of Richtek Technology Corporation.

of the short circuit OCP is designed 1.5 times of normal OCP level. Hence, the equation of short circuit OCP threshold is:

$$I_{LX(MAX), \; short} \; = 1.5 \; x \; I_{LX(MAX)} = 3 \times \frac{V_{IMAX}}{R_{IMAX}} \times \frac{R_{CSNX}}{DCR_X}, \label{eq:local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local$$

and the delay of short circuit OCP is 20µs. when short circuit OCP is triggered, the RT8868 will turn off both high side MOSFET and low side MOSFET of all channels.

#### **CORE Section Over Voltage Protection (OVP)**

The over voltage protection monitors the output voltage via the FB pin. Once VFB exceeds 1.8V, OVP is triggered and latched for VCORE section. RT8868 will try to turn on each low side MOSFET and turn off each high side MOSFET to protect CPU.

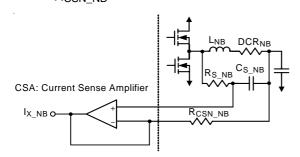

#### **NB Section Output Current Sensing**

The RT8868 provides low input offset Current Sense Amplifier (CSA) to monitor the continuous output current of NB section. Output current of CSA (IX NB) is used for over current detection as shown in Figure 12. In this inductor current sensing topology, R<sub>S NB</sub> and C<sub>S NB</sub> must be set according to the equation below:

$$\frac{L_{NB}}{DCR_{NB}} = R_{S\_NB} \times C_{S\_NB}$$

Then the output current of CSA will follow the equation

$$I_{X\_NB} = \frac{I_{L\_NB} \times DCR_{NB}}{R_{CSN\_NB}}$$

Figure 12. Current Sensing Circuit for NB Section

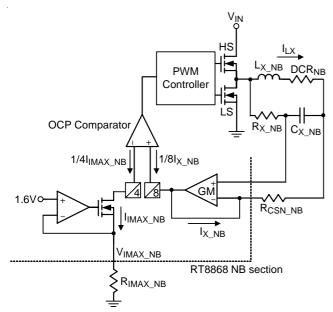

#### **NB Section Over Current Protection (OCP)**

NB section uses an external resistor R<sub>IMAX NB</sub> connected to IMAX\_NB pin to generate a reference current I<sub>MAX\_NB</sub> for over current protection as depicted in Figure 13.

$$I_{IMAX\_NB} = \frac{V_{IMAX\_NB}}{R_{IMAX\_NB}}$$

where V<sub>IMAX NB</sub> is typically 1.6V. The OCP comparator compares the sensed phase current  $I_{X\ NB}$  with the reference current. Equivalently, the maximum phase NB current I<sub>LX NB(MAX)</sub> is calculated as below:

$$\begin{split} \frac{1}{4} \times I_{IMAX\_NB} &= \frac{1}{8} \times I_{X\_NB} \\ I_{X\_NB} &= 2 \times I_{IMAX\_NB} = 2 \times \frac{V_{IMAX\_NB}}{R_{IMAX\_NB}} \\ I_{LX\_NB(MAX)} &= I_{X\_NB} \times \frac{R_{CSN\_NB}}{DCR_{NB}} \\ &= 2 \times \frac{V_{IMAX\_NB}}{R_{IMAX\_NB}} \times \frac{R_{CSN\_NB}}{DCR_{NB}} \end{split}$$

Once  $I_{X\_NB}$  is larger than 2 x  $I_{IMAX\_NB}$ , OCP of NB section is triggered and latched. Then, the RT8868 will turn off both high side MOSFET and low side MOSFET of NB section. A 100µs delay is used in OCP detection circuit to prevent false trigger.

Except the normal OCP function described above, there is another short circuit OCP function especially designed for short circuit protection. Since short circuit may cause catastrophic damage over a very short period, the short circuit OCP should have a very short delay for triggering OCP latch. Also to prevent false trigger, the trigger level of the short circuit OCP is designed 1.5 times of normal OCP level of NB section. Hence, the equation of NB section short circuit OCP threshold is :

$$\begin{split} I_{LX\_NB(MAX), \ short} &= 1.5 \ x \ I_{LX\_NB(MAX)} \\ &= 3 \times \frac{V_{IMAX\_NB}}{R_{IMAX\_NB}} \times \frac{R_{CSN\_NB}}{DCR_{NB}}, \end{split}$$

and the delay of short circuit OCP of NB section is 20µs. When short circuit OCP is triggered at NB section, the RT8868 will turn off both high side MOSFET and low side MOSFET of NB section.

Figure 13. Over Current Protection for NB Section

#### **NB Section Over Voltage Protection (OVP)**

The over voltage protection monitors the output voltage via the FB\_NB pin. Once  $V_{FB\_NB}$  exceeds 1.8V, OVP is triggered and latched for NB section. The RT8868 will try to turn on low side MOSFET and turn off high side MOSFET to protect NB.

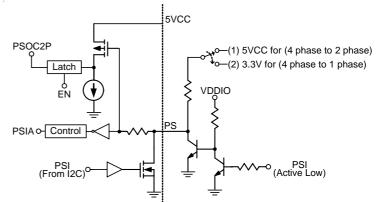

#### **Power Saving Indicator (PSI)**

This is an active low flag that can be set by the CPU to allow the regulator to enter Power-Saving mode to maximize the system efficiency when in light-load conditions. The status of the flag is communicated to the controller through either the SVI bus or PS pin. The RT8868 monitors the PS pin to define the action performed by the controller when PSI is asserted.

According to Figure 14, by programming different voltage on PS pin, this configures the controller to operate in one or two-phase condition when PSI is asserted. By pulling up PS pin to 3.3V through a resistor, the controller operates in only one-phase configuration. If the 3.3V is changed to 5V, the RT8868 operates in two-phase configuration. When PSI is de-asserted, the controller will return to the original configuration. The PSI strategy is summarized as shown in Table 5.

Figure 14. Power-Saving-Mode Circuit

### Table 5. PSI Strategy

| PS pin            | PSI Strategy                   |  |  |

|-------------------|--------------------------------|--|--|

| Dull lin to 2 2\/ | Phase number is set to 1 while |  |  |

| Pull-Up to 3.3V   | PSI is asserted.               |  |  |

| Dull the te 51/   | Phase number is set to 2 while |  |  |

| Pull-Up to 5V     | PSI is asserted.               |  |  |

#### **Non-overlap Control of MOSFET Driver**

To prevent the overlap of the gate drives during the UGATE pull low and the LGATE pull high, the non-overlap circuit monitors the voltages at the PHASE node and high side gate drive (UGATE-PHASE). When the PWM input signal goes low, UGATE begins to pull low (after propagation delay). Before LGATE can pull high, the non-overlap protection circuit ensures that the monitored voltages have gone below 1.1V. Once the monitored voltages fall below 1.1V, LGATE begins to turn high. By waiting for the voltages of the PHASE pin and high side gate drive to fall below 1.1V, the non-overlap protection circuit ensures that UGATE is low before LGATE pulls high.

Also to prevent the overlap of the gate drives during LGATE pull low and UGATE pull high, the non-overlap circuit monitors the LGATE voltage. When LGATE go below 1.1V, UGATE goes high after propagation delay.

### **Layout Considerations**

Careful PCB layout is critical to achieve low switching losses and clean, stable operation. The high power switching power stage requires particular attention. Follow these guidelines for optimum PCB layout.

Place the power components first, including power MOSFETs, input and output capacitors, and inductors. It is important to have a symmetrical layout for each power train, preferably with the controller located equidistant from each. Symmetrical layout allows heat to be dissipated equally across all power trains. Great attention should be paid for routing the UGATE, LGATE, and PHASE traces since they drive the power train MOSFETs with short, high current pulses. It is important to size them as large and short as possible to reduce their overall impedance and inductance. Extra care should be given to the LGATE traces in particular since keeping their impedance and inductance low helps to significantly reduce the possibility of shoot through.

When placing the MOSFETs, try to keep the source of the upper MOSFETs and the drain of the lower MOSFETs as close to each other as possible. Input bulk capacitors should be placed close to the drain of the upper MOSFETs and the source of the lower MOSFETs.

Locate the output inductors and output capacitors between the MOSFETs and the load. Route high-speed switching nodes away from sensitive analog areas (ISP, ISN, FB, FBRTN, COMP, ADJ, OFS, IMAX.....)

Keep the routing of the bootstrap capacitor short between BOOT and PHASE.

Place the snubber R&C as close as possible to the lower MOSFETs of each phase.

#### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

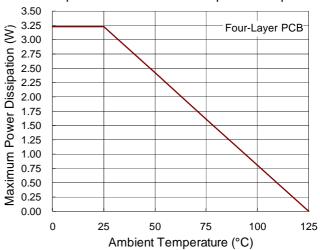

For recommended operating condition specifications of the RT8868, the maximum junction temperature is 125°C and  $T_A$  is the ambient temperature. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For WQFN-48L 7x7 packages, the thermal resistance,  $\theta_{JA}$ , is 31°C/W on a standard JEDEC 51-7 four-layer thermal test board. The maximum power dissipation at  $T_A = 25$ °C can be calculated by the following formula :

$$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (31^{\circ}C/W) = 3.226W$$

for

WQFN-48L 7x7 package

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ . For RT8868 package, the derating curve in Figure 15 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 15. Derating Curves for RT8868 Package

DS8868-05 January 2014

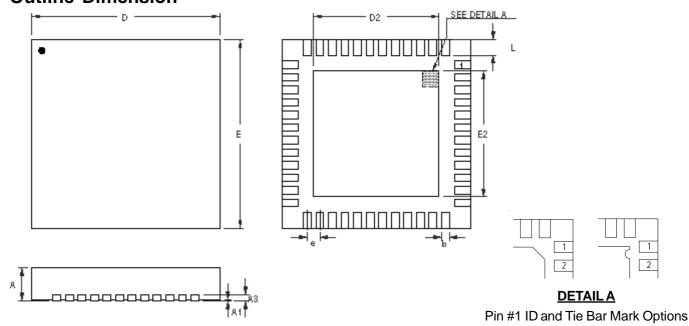

### **Outline Dimension**

Note: The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| 0      | Dimensions | In Millimeters | Dimensions In Inches |       |  |

|--------|------------|----------------|----------------------|-------|--|

| Symbol | Min        | Max            | Min                  | Max   |  |

| А      | 0.700      | 0.800          | 0.028                | 0.031 |  |

| A1     | 0.000      | 0.050          | 0.000                | 0.002 |  |

| A3     | 0.175      | 0.250          | 0.007                | 0.010 |  |

| b      | 0.200      | 0.300          | 0.008                | 0.012 |  |

| D      | 6.950      | 7.050          | 0.274                | 0.278 |  |

| D2     | 5.050      | 5.250          | 0.199                | 0.207 |  |

| Е      | 6.950      | 7.050          | 0.274                | 0.278 |  |

| E2     | 5.050      | 5.250          | 0.199                | 0.207 |  |

| е      | 0.5        | 500            | 0.0                  | )20   |  |

| L      | 0.350      | 0.450          | 0.014                | 0.018 |  |

W-Type 48L QFN 7x7 Package

### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

DS8868-05 January 2014 www.richtek.com