#### **General Description**

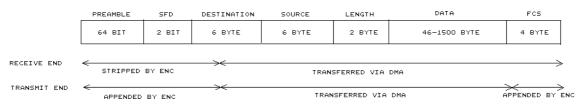

The DM9008 Ethernet controller is a highly integrated design provides all Medial Access Control that (MAC) and Encode-Decode (ENDEC) functions in accordance with 802.3 the IEEE Network interfaces standard. include 10BASE5 or 10BASE2 Ethernet via the AUI port and 10BASE-T via the Twisted-pair. The DM9008 Ethernet controller can interface directly to the PC-AT ISA bus without any external device. The interface to PC-AT ISA bus is fully compatible with NE2000 Ethernet

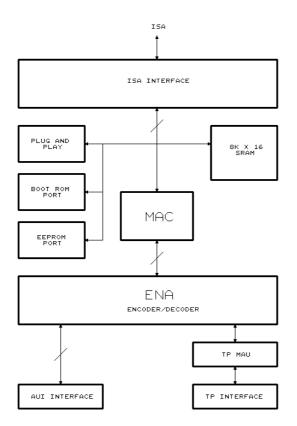

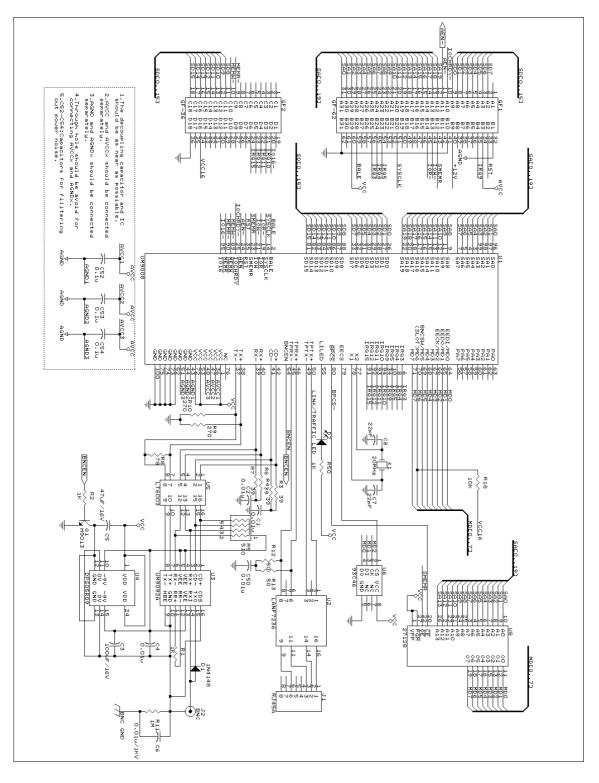

#### **Block Diagram**

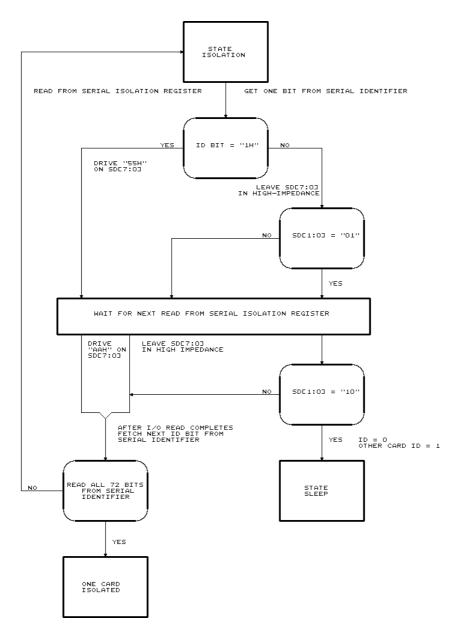

adapter cards, so all software programs designed for NE2000 can run on the DM9008 card without any modification. Microsoft's Plug and Play and the jumperless software configuration function are both supported. The capability of the PnP and Non-PnP mode auto-switch function allows users to configure network card. No jumpers or switches are needed to set when using either the PC or PnP function. The integrated 8Kx16 SRAM and 10BASE-T transceiver make DM9008 more cost-effective.

#### Features

- Single chip solution for IEEE 802.3, 10BASE-T, 10BASE2 and 10BASE5

- Integrated ISA interface, 8Kx16 SRAM, Media Access Control, ENDEC and 10BASE-T transceiver

- Supports ISA Plug and Play configuration

- Software-compatible with NOVELL NE2000

- Supports PnP and Non-PnP Auto-switching

- PnP, Non-PnP and Auto-switch mode software selectable

- 8 interrupt lines selectable

- Auto-Polarity detection and correction

- Selectable 8 and 16-bit slot mode

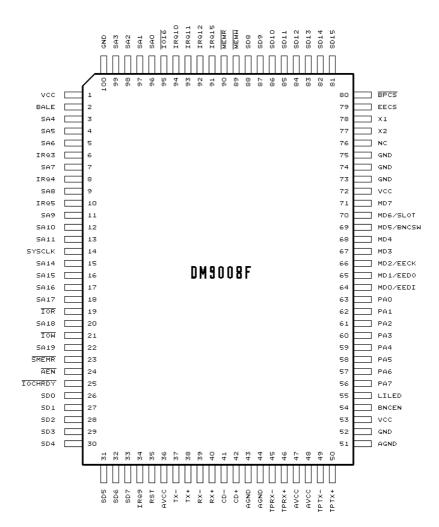

#### **Pin Configuration**

- Provides auto-detection/auto-switching for 10BASE-T Transceiver and Attachment Unit Interface (AUI)

- External EEPROM programmable

- Supports BOOT-ROM page mode

- Loopback capability for diagnostics

- Receiver and collision squelch circuit to reduce noise

- Low-power CMOS process with single 5V power supply

- Built-in pre-distortion resisters for 10BASE-T application

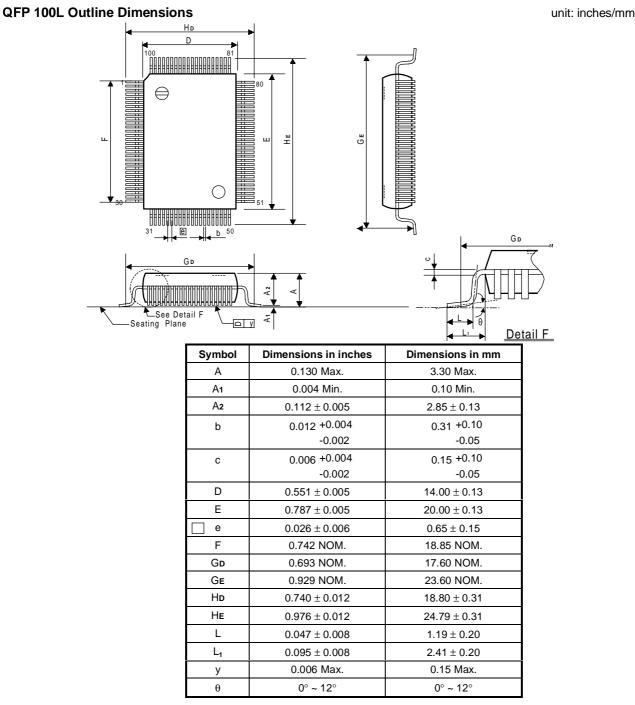

- 100-pin QFP package

#### **Absolute Maximum Ratings\***

#### \*Comments

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to this device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied or intended. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.

| <b>DC Electrical Characteristics</b> | (VCC = 5V $\pm$ 5%, Tc= 0°C to 85°C, unless otherwise specified) |

|--------------------------------------|------------------------------------------------------------------|

|--------------------------------------|------------------------------------------------------------------|

| Symbol      | Parameter                                       | Min.             | Max.       | Unit   | Conditions                                       |  |

|-------------|-------------------------------------------------|------------------|------------|--------|--------------------------------------------------|--|

| Voh         | High Level Output Voltage<br>(Notes 1, 2)       | VCC - 0.1<br>3.5 |            | V<br>V | loh = -20μA<br>loh = -2.0mA                      |  |

| Vol         | Low Level Output Voltage<br>(Notes 1, 2)        |                  | 0.1<br>0.4 | V<br>V | lol = 20μA<br>lol = 2.0mA                        |  |

| Vih         | High Level Input Voltage (Note 6)               | 3.0              |            | V      |                                                  |  |

| Vil         | Low Level Input Voltage (Note 6)                |                  | 0.8        | V      |                                                  |  |

| lin         | Input Current                                   | -1.0             | +1.0       | μΑ     | Vi = VCC or GND                                  |  |

| loz         | Tri-state Output Leakage Current                | -10              | +10        | μA     | Vout = VCC or GND                                |  |

| lcco        | Operating VCC + AVCC Supply<br>Current (Note 3) |                  | 120        | mA     | X1 = 20 Mhz<br>lout = 0μA                        |  |

| lccs        | Standby VCC + AVCC Supply<br>Current (Note 4)   |                  | 110        | mA     | Vin = VCC or GND                                 |  |

| Differentia | I Pins (TX+/TX-, RX+/RX-, CD+/CD)               |                  |            |        |                                                  |  |

| Vod         | Differential Output Voltage (TX±)               | +550             | +1200      | mV     | 78 ohm termination and 270 ohms from each to GND |  |

| Vов         | Differential Output Voltage<br>Imbalance (TX±)  |                  | 40         | mV     | 78 ohm termination and 270 ohms from each to GND |  |

| Vu          | Undershoot Voltage (TX±)                        |                  | 100        | mV     | 78 ohm termination and 270 ohms from each to GND |  |

# DM9008

ISA/Plug & Play Super Ethernet Contoller

## **DC Electrical Characteristics (continued)**

| Symbol     | Parameter                                                        | Min.             | Max.     | Unit   | Conditions |

|------------|------------------------------------------------------------------|------------------|----------|--------|------------|

| VDS        | Differential Squelch Threshold (RX± and CD±)                     | -175<br>(Note 5) | -300     | mV     |            |

| VCM        | Differential Input Common Mode<br>Voltage (RX± and CD±) (Note 5) | 0                | 5.5      | V      |            |

| Twisted Pa | Twisted Pair Interface Pins (TPTX+/TPTX-)                        |                  |          |        |            |

| Vtidf      | TP input voltage                                                 | .350             | 2.0      | V      | -          |

| Vil<br>Vih | LI:<br>low<br>high                                               | -<br>2.4         | 0.8<br>- | V<br>V | -          |

Note 1: These levels are tested dynamically using a limited number of functional test patterns. Refer to AC Test Load. Note 2: The low drive CMOS compatible Voh and Vol limits are not tested directly. Detailed device characterization verifies that this specification can be guaranteed by testing the high drive TTL compatible Vol and Voh specifications.

Note 3: This measurement is made while the DM9008 is undergoing transmission, reception, and collision. The value is not measured instantaneously, but is averaged over a span of several milliseconds.

Note 4: This measurement is made while the DM9008 is sitting idle of transmission. This measurement is described in note 1.

Note 5: This parameter is guaranteed by design and is not tested.

Note 6: Except RST, IORB, IOWB which are Schmitt trigger with Vil = 1.0V, Vih = 2.8V.

## **Pin Description**

| Pin No.                                                    | Symbol                                                                          | I/O    | Description                                                                                                                                                                                           |  |  |

|------------------------------------------------------------|---------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PC ISA BUS IN                                              | PC ISA BUS INTERFACE PINS                                                       |        |                                                                                                                                                                                                       |  |  |

| 96 - 99<br>3 - 5<br>7<br>9<br>11 - 13<br>15 - 18<br>20, 22 | SA0 - SA3<br>SA4 - SA6<br>SA7<br>SA8<br>SA9 - SA11<br>SA14 - SA17<br>SA18, SA19 | I      | SYSTEM ADDRESS: These signals are connected to the address<br>bus of the PC I/O slot. They are used to select the DM9008 I/O ports<br>or the boot ROM address                                         |  |  |

| 26 - 33<br>88 - 81                                         | SD0 - SD7<br>SD8 - SD15                                                         | I/O, Z | SYSTEM DATA: These signals are connected to the data bus of the PC I/O bus slot. They are used to transfer data between the PC and the DM9008                                                         |  |  |

| 2                                                          | BALE                                                                            | I      | ADDRESS LATCH ENABLE: PC ISA bus BALE signal; used only to define the timing of IOCHRDY in Remote DMA<br>This pin is not used if the value of biteA of CRB is 0, and tie to high to prevent floating. |  |  |

| 14                                                         | SYSCLK                                                                          | I      | SYSTEM CLOCK: PC ISA bus system clock<br>This pin is not used if the value of biteA of CRB is 0, and tie to high to<br>prevent floating.                                                              |  |  |

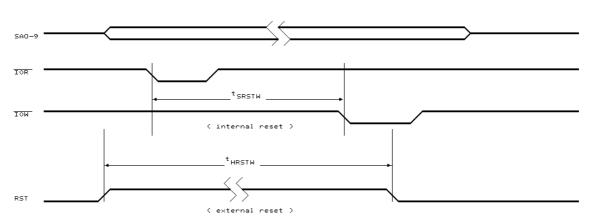

| 19                                                         | ĪOR                                                                             | I      | I/O READ: An active low signal used to read data from the DM9008                                                                                                                                      |  |  |

| 21                                                         | ĪOW                                                                             | I      | I/O WRITE: An active low signal used to write data to the DM9008                                                                                                                                      |  |  |

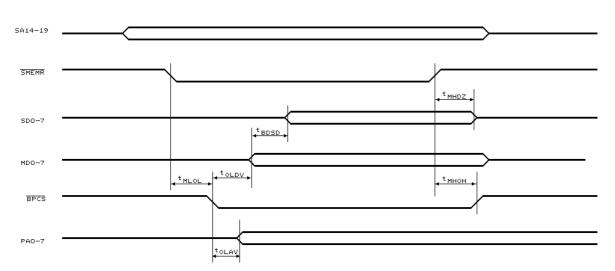

| 23                                                         | SMEMR                                                                           | I      | MEMORY READ: An active low signal used to read boot ROM data                                                                                                                                          |  |  |

| 35                                                         | RST                                                                             | I      | RESET: An active high signal used to power-on reset the DM9008                                                                                                                                        |  |  |

| 24                                                         | AEN                                                                             | Ι      | ADDRESS ENABLE: This is an active low signal used to enable the system address for the DM9008                                                                                                         |  |  |

| 25                                                         | IOCHRDY                                                                         | O I, Z | I/O CHANNEL READY: The DM9008 sets this signal low to insert wait states into the PC ISA bus                                                                                                          |  |  |

| 89                                                         | MEMW                                                                            | I      | MEMORY WRITE: PC ISA bus memory write signal<br>This pin is not used if the value of biteA of CRB is 0, and tie to high to<br>prevent floating.                                                       |  |  |

| 90                                                         | MEMR                                                                            |        | MEMORY READ: PC ISA bus memory read signal<br>This pin is not used if the value of biteA of CRB is 0, and tie to high to<br>prevent floating.                                                         |  |  |

| 95                                                         | IO16                                                                            | O, Z   | 16-BIT I/O: This signal goes low when the data transfer between the DM9008 and the PC ISA bus is word wide                                                                                            |  |  |

# DM9008

ISA/Plug & Play Super Ethernet Contoller

| -                                   |                                                   |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------|---------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>8<br>10<br>34<br>94 - 92<br>91 | IRQ3<br>IRQ4<br>IRQ5<br>IRQ9<br>IRQ10-12<br>IRQ15 | O, Z   | INTERRUPT REQUESTS: These are 8 interrupt request pins. Only<br>one pin, which is decoded from Configuration Register A, can be<br>activated; the other pins are left floating. The activated pin will go<br>high when an interrupt request is generated from the ENC module of<br>the DM9008                                                                                                                                                        |

| MEMORY INTE                         | ERFACE PINS                                       |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 79                                  | EECS                                              | 0      | EEPROM CHIP SELECT: This signal goes high when the EEPROM is selected by the DM9008                                                                                                                                                                                                                                                                                                                                                                  |

| 80                                  | BPCS                                              | 0      | BOOT ROM CHIP SELECT: This signal goes low when the PC reads the boot ROM data                                                                                                                                                                                                                                                                                                                                                                       |

| 64 - 71                             | MD0 - MD7                                         | I/O, Z | MEMORY DATA BUS: These are the memory data signals for the boot ROM<br>When the EEPROM is loaded or written, MD0, 1, 2 are used as the                                                                                                                                                                                                                                                                                                               |

| (64)                                | (EEDI)                                            |        | EEPROM signals<br>* EEPROM DATA IN: This pin is used as the serial input data                                                                                                                                                                                                                                                                                                                                                                        |

| (65)                                | (EEDO)                                            |        | signal from the EEPROM<br>* EEPROM DATA OUT: This pin is used as the serial output data<br>signal to the EEPROM                                                                                                                                                                                                                                                                                                                                      |

| (66)                                | (EECK)                                            |        | * EEPROM CLOCK: This pin is used as the EEPROM clock signal                                                                                                                                                                                                                                                                                                                                                                                          |

| (66)<br>(69)<br>(70)                | (LEDSW)<br>(BNCSW)<br>(SLOT)                      |        | These memory data pins can also be used as switches when the DM9008 is in reset state. There is an approximately 100K pull-low resistor on each pin, and a 10K pull-high resistor can be connected to a pin when it is switched to logic high LED mode switch: see page 67 for details.<br>* When this pin pulled high upon reset, pin 54 outputs 312.5KHz<br>* SLOT SELECTION: When this pin is pulled to high, the DM9008 is in NE2000 16-bit mode |

| 63 - 56                             | PA0 - PA7                                         | 0      | BOOT ROM PAGE ADDRESS. When the boot ROM is accessed, PA0-PA7 are used as the page address of the boot ROM                                                                                                                                                                                                                                                                                                                                           |

| NETWORK INT                         | FERFACE PINS                                      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

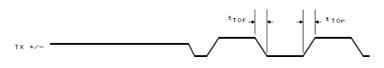

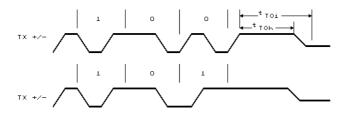

| 37<br>38                            | TX-<br>TX+                                        | 0      | TRANSMIT OUTPUT: Differential line driver which sends the encoded data to the transceiver. The outputs are source followers which require 270 ohm pull-down resistors                                                                                                                                                                                                                                                                                |

| 54                                  | BNCEN                                             | 0      | BNC OUTPUT ENABLE: This pin goes high if the value of the<br>Configuration Register B bit 1 is low and bit 0 is high. Typically, this<br>pin is used to control the DC-DC converter to enable or disable the<br>UM9092A (Coaxial Transceiver Interface)<br>* Output 312.5KHz clock: when the 69 pin (BNCSW) is pulled high,<br>this pin output 312.5KHz clock                                                                                        |

| 78                                  | X1                                                | 0      | CRYSTAL FEEDBACK OUTPUT: Used in crystal connection only.<br>Connect to ground when using an external clock                                                                                                                                                                                                                                                                                                                                          |

| 77                                  | X2                                                | I      | CRYSTAL or EXTERNAL CLOCK INPUT                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B                                   | 1                                                 | 1      |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

## **Pin Description (continued)**

| Pin No.                | Symbol                 | I/O           | Description                                                                                                                                                                                               |  |  |

|------------------------|------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NETWORK INT            | NETWORK INTERFACE PINS |               |                                                                                                                                                                                                           |  |  |

| 39<br>40               | RX-<br>RX+             | I             | RECEIVE INPUT: Differential receive input pair from the transceiver                                                                                                                                       |  |  |

| 41<br>42               | CD-<br>CD+             | I             | COLLISION INPUT: Differential collision input pair from the transceiver                                                                                                                                   |  |  |

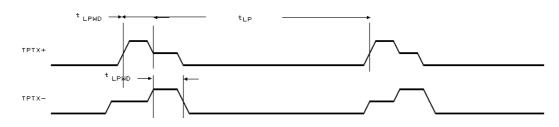

| 50<br>49               | TPTX+<br>TPTX-         | 0             | TP Driver Outputs. These two outputs provide the TP drivers with pre-distortion capability                                                                                                                |  |  |

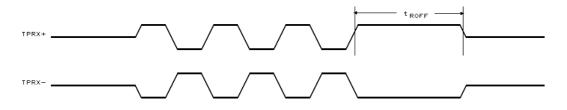

| 46<br>45               | TPRX+<br>TPRX-         | I             | TP Receive Input. A differential receiver tie to the receive transformer pair of the twisted-pair wire.<br>The receive pair of the twisted-pair medium is driven with 10 Mbits/s Manchester-encoded data  |  |  |

| 5                      | LILED                  | OPEN<br>DRAIN | LINK and Traffic LED Driver: If TP is LINK-pass, this pin outputs low.<br>This pin will go low for 80ms and then into high impedance state for<br>50ms to indicate the presence of traffic on the network |  |  |

| 76                     | NC                     |               | No connection                                                                                                                                                                                             |  |  |

| POWER SUPP             | LY PINS                |               |                                                                                                                                                                                                           |  |  |

| 36, 47, 48             | AVCC                   |               | +5V DC power supply for analog CKT. A decoupling capacitor should be connected between these pins and GND for analog CKT                                                                                  |  |  |

| 43, 44, 51             | AGND                   |               | GND for analog CKT                                                                                                                                                                                        |  |  |

| 1, 53, 72              | VCC                    |               | +5V DC power supply for digital CKT. A decoupling capacitor should be connected between these pins and GND for digital CKT                                                                                |  |  |

| 52, 73, 74,<br>75, 100 | GND                    |               | GND for digital CKT                                                                                                                                                                                       |  |  |

# **ENC Register Address Assignments**

# Page 0 (PS1 = 0, PS0 = 0)

| SA0-SA3 | RD                                                      | WR                                            |

|---------|---------------------------------------------------------|-----------------------------------------------|

| 00H     | Command (CR)                                            | Command (CR)                                  |

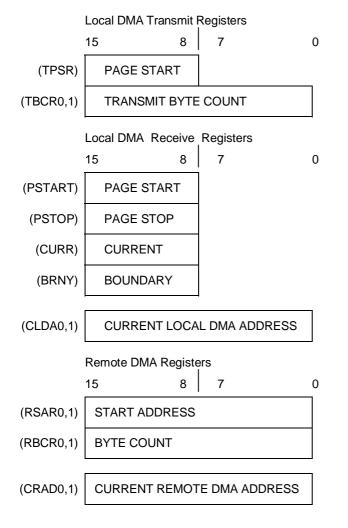

| 01H     | Current Local DMA<br>Address 0 (CLDA0)                  | Page Start Register<br>(PSTART)               |

| 02H     | Current Local DMA<br>Address 1 (CLDA1)                  | Page Stop Register<br>(PSTOP)                 |

| 03H     | Boundary Pointer<br>(BNRY)                              | Boundary<br>Pointer(BNRY)                     |

| 04H     | Transmit Status<br>Register (TSR)                       | Transmit Page Start<br>Address (TPSR)         |

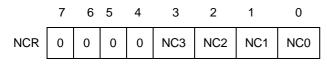

| 05H     | Number of<br>Collisions Register<br>(NCR)               | Transmit Byte<br>Count Register 0<br>(TBCR0)  |

| 06H     | FIFO                                                    | Transmit Byte<br>Count Register 1<br>(TBCR1)  |

| 07H     | Interrupt Status<br>Register (ISR)                      | Interrupt Status<br>Register (ISR)            |

| 08H     | Current Remote<br>DMA Address 0<br>(CRDA0)              | Remote Start<br>Address Register 0<br>(RSAR0) |

| 09H     | Current Remote<br>DMA Address 1<br>(CRDA1)              | Remote Start<br>Address Register 1<br>(RSAR1) |

| 0AH     | Configuration<br>Register A                             | Remote Byte Count<br>Register 0 (RBCR0)       |

| 0BH     | Configuration<br>Register B                             | Remote Byte Count<br>Register 1 (RBCR1)       |

| 0CH     | Receive Status<br>Register (RSR)                        | Receive Configura-<br>tion Register (RCR)     |

| 0DH     | Tally Counter 0<br>(Frame AlignmentÞ<br>Errors) (CNTR0) | Transmit<br>Configuration<br>Register (TCR)   |

| 0EH     | Tally Counter 1<br>(CRC Errors)<br>(CNTR1)              | Data Configuration<br>Register (DCR)          |

| 0FH     | Tally Counter 2<br>(Missed Packet<br>Errors) (CNTR2)    | Interrupt Mask<br>Register (IMR)              |

# Page 1 (PS1 = 0, PS0 = 1)

| SA0-SA3 | RD                                     | WR                                       |

|---------|----------------------------------------|------------------------------------------|

| 00H     | Command (CR)                           | Command (CR)                             |

| 01H     | Physical Address<br>Register 0 (PAR0)  | Physical Address<br>Register 0 (PAR0)    |

| 02H     | Physical Address<br>Register 1 (PAR1)  | Physical Address<br>Register 1 (PAR1)    |

| 03H     | Physical Address<br>Register 2 (PAR2)  | Physical Address<br>Register 2 (PAR2)    |

| 04H     | Physical Address<br>Register 3 (PAR3)  | Physical Address<br>Register 3 (PAR3)    |

| 05H     | Physical Address<br>Register 4 (PAR4)  | Physical Address<br>Register 4 (PAR4)    |

| 06H     | Physical Address<br>Register 5 (PAR5)  | Physical Address<br>Register 5 (PAR5)    |

| 07H     | Current Page<br>Register (CURR)        | Current Page<br>Register (CURR)          |

| 08H     | Multicast Address<br>Register 0 (MAR0) | Register 0<br>(MAR0)Multicast<br>Address |

| 09H     | Multicast Address<br>Register 1 (MAR1) | Multicast Address<br>Register 1 (MAR1)   |

| 0AH     | Multicast Address<br>Register 2 (MAR2) | Multicast Address<br>Register 2 (MAR2)   |

| 0BH     | Multicast Address<br>Register 3 (MAR3) | Multicast Address<br>Register 3 (MAR3)   |

| 0CH     | Multicast Address<br>Register 4 (MAR4) | Multicast Address<br>Register 4 (MAR4)   |

| 0DH     | Multicast Address<br>Register 5 (MAR5) | Multicast Address<br>Register 5 (MAR5)   |

| 0EH     | Multicast Address<br>Register 6 (MAR6) | Multicast Address<br>Register 6 (MAR6)   |

| 0FH     | Multicast Address<br>Register 7 (MAR7) | Multicast Address<br>Register 7 (MAR7)   |

# **Register Address Assignments (continued)**

# Page 2 (PS1 = 1, PS0 = 0)

| SA0-SA3          | RD                                 | WR                                     |

|------------------|------------------------------------|----------------------------------------|

| 00H              | Command (CR)                       | Command (CR)                           |

| 01H <sup>3</sup> | Page Start<br>Register (PSTART)    | Current Local DMA<br>Address 0 (CLDA0) |

| 02H              | Page Stop<br>Register (PSTOP)      | Current Local DMA<br>Address 1 (CLDA1) |

| 03H              | Remote Next<br>Packet Pointer      | Remote Next<br>Packet Pointer          |

| 04H              | Transmit Page<br>Start Address     |                                        |

| 05H              | Local Next Packet                  | Local Next Packet                      |

| 06H              | Address Counter<br>(Upper)         | Address Counter<br>(Upper)             |

| 07H              | Address Counter<br>(Lower)         | Address Counter<br>(Lower)             |

| 08H              |                                    |                                        |

| 09H              | Interrupt Lines<br>Status Register | Interrupt Lines<br>Pull-Down Register  |

| 0AH              | Boot ROM Page<br>Register          | Boot ROM Page<br>Register              |

| SA0-SA3 | RD                                          | WR                          |

|---------|---------------------------------------------|-----------------------------|

| 0BH     | Configuration<br>Register C                 | Configuration<br>Register C |

| 0CH     | Receive<br>Configuration<br>Register (RCR)  |                             |

| 0DH     | Transmit<br>Configuration<br>Register (TCR) |                             |

| 0EH     | Data Configuration<br>Register (DCR)        |                             |

| 0FH     | Interrupt Mask<br>Register (IMR)            |                             |

#### Page3 (PS1=1, PS0=1)

| SA0-SA3 | RD                          | WR                          |

|---------|-----------------------------|-----------------------------|

| 00H     | Command (CR)                | Command (CR)                |

| 01H-06H |                             |                             |

| 07H     | Configuration<br>Register D | Configuration<br>Register D |

| 08H-0FH |                             |                             |

# **Register Descriptions**

# **Configuration Register A (CRA)**

Configuration Register A can be read at address 0AH in Page 0 of ENC, and can be written by following a read to address 0AH with a write to address 0AH. If address 0AH is written without a previous read to 0AH, the write will be regarded as a write to register RBCR0 of ENC.

| 7     | 6    | 5    | 4    | 3     | 2     | 1     | 0     |

|-------|------|------|------|-------|-------|-------|-------|

| FREAD | INT2 | INT1 | INT0 | IOAD3 | IOAD2 | IOAD1 | IOAD0 |

| Bit   | Symbol |           |              |             | I            | Description   |                                          |

|-------|--------|-----------|--------------|-------------|--------------|---------------|------------------------------------------|

| 0 - 3 | IOAD0  |           |              | e three bit | s determine  | the base I/0  | D address of DM9008 within the PC        |

|       | IOAD1  |           | I/O map      |             |              |               |                                          |

|       | IOAD2  | bit3      | bit2         | bit1        | bit0         | I/O base      |                                          |

|       | IOAD3  | 0         | 0            | 0           | 0            | 300H          |                                          |

|       |        | 0         | 0            | 0           | 1            | 320H          |                                          |

|       |        | 0         | 0            | 1           | 0            | 340H          |                                          |

|       |        | 0         | 0            | 1           | 1            | 360H          |                                          |

|       |        | 0         | 1            | 0           | 0            | 380H          |                                          |

|       |        | 0         | 1            | 0           | 1            | 3A0H          |                                          |

|       |        | 0         | 1            | 1           | 0            | 3C0H          |                                          |

|       |        | 0         | 1            | 1           | 1            | 3E0H          |                                          |

|       |        | bit3      | bit2         | bit1        | bit0         | I/O base      |                                          |

|       |        | 1         | 0            | 0           | 0            | 200H          |                                          |

|       |        | 1         | 0            | 0           | 1            | 220H          |                                          |

|       |        | 1         | 0            | 1           | 0            | 240H          |                                          |

|       |        | 1         | 0            | 1           | 1            | 260H          |                                          |

|       |        | 1         | 1            | 0           | 0            | 280H          |                                          |

|       |        | 1         | 1            | 0           | 1            | 2A0H          |                                          |

|       |        | 1         | 1            | 1           | 0            | 2C0H          |                                          |

|       |        | 1         | 1            | 1           | 1            | 2E0H          |                                          |

| 4 - 6 | INT0   | Interrupt | Pin Mapp     | ing: Only   | one interrup | ot output pin | will be driven active when a valid       |

|       | INT1   | interrupt | condition    | occurs      |              |               |                                          |

|       | INT2   | bit5      | bit4         | bit3        | Interrupt    |               |                                          |

|       |        | 0         | 0            | 0           | IRQ3         |               |                                          |

|       |        | 0         | 0            | 1           | IRQ4         |               |                                          |

|       |        | 0         | 1            | 0           | IRQ5         |               |                                          |

|       |        | 0         | 1            | 1           | IRQ9         |               |                                          |

|       |        | 1         | 0            | 0           | IRQ10        |               |                                          |

|       |        | 1         | 0            | 1           | IRQ11        |               |                                          |

|       |        | 1         | 1            | 0           | IRQ12        |               |                                          |

|       |        | 1         | 1            | 1           | IRQ15        |               |                                          |

| 7     | FREAD  | Fast Rea  | ad: In the r | emote DN    | /IA read mod | le. When this | s bit is set high, the DM9008 will begin |

| -     |        |           |              |             |              | R is complet  |                                          |

|       |        | the next  | Port leton   |             |              |               |                                          |

# Configuration Register B (CRB)

Configuration Register B can be read at address 0BH in Page 0 of ENC, and can be written by following a read to address 0BH with a write to address 0BH. If a write to address 0BH is performed without a previous read to 0BH, it will be regarded as a write to register RBCR1 of ENC.

|   | 7 | 6 | 5      | 4     | 3 | 2      | 1     | 0     |

|---|---|---|--------|-------|---|--------|-------|-------|

| Ĩ |   |   | BUSERR | CHRDY |   | GDLINK | PHYS1 | PHYS0 |

| Bit  | Symbol         | Description                                                                                                                                                                                                                        |

|------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0, 1 | PHYS0<br>PHYS1 | Physical Media Interfaces: These two bits determine which type of physical interface theDM9008 is using, as shown below:bit1bit0Interface000Set to 10BASE-T; BNCEN = low0101102Set to 10BASE5; BNCEN = high111Auto-detection media |

| 2    | GDLINK         | Read: Link status. One indicates Link OK; zero indicates Link Fail                                                                                                                                                                 |

| 3    |                | Reserved                                                                                                                                                                                                                           |

| 4    | CHRDY          | IOCHRDY from $\overline{IOR}$ or $\overline{IOW}$ or from BALE: When low, DM9008 will pull IOCHRDY low after the command strobe. If high, IOCHRDY will be pulled low after BALE goes high                                          |

| 5    | BUSERR         | Bus Error: This bit shows that DM9008 has detected an ISA bus error. This bit will be high if DM9008 inserts wait states into a system access and the system terminates the cycle without inserting wait states                    |

| 6    |                | Reserved                                                                                                                                                                                                                           |

| 7    |                | Reserved                                                                                                                                                                                                                           |

# Configuration Register C (CONFIG.C)

This register is configured during RESET and EEPROM read states. CONFIG.C can be read from address 0BH of page 2 of ENC.

| 7 | 6   | 5 | 4 | 3    | 2    | 1    | 0    |

|---|-----|---|---|------|------|------|------|

|   | PnP |   |   | BPS3 | BPS2 | BPS1 | BPS0 |

| Bit   | Symbol<br>BPS0<br>BPS1 |          | Description                                                                     |            |               |                 |                  |  |  |  |  |

|-------|------------------------|----------|---------------------------------------------------------------------------------|------------|---------------|-----------------|------------------|--|--|--|--|

| 0 - 3 |                        | BOOT P   | BOOT PROM Select: Selects address at which boot ROM begins and size of boot ROM |            |               |                 |                  |  |  |  |  |

|       | BPS2                   | bit3     | bit2                                                                            | bit1       | bit0          | Address         | Size             |  |  |  |  |

|       | BPS3                   | 0        | 0                                                                               | 0          | Х             | X               | No boot ROM      |  |  |  |  |

|       |                        | 0        | 0                                                                               | 1          | 0             | C0000H          | 16K              |  |  |  |  |

|       |                        | 0        | 0                                                                               | 1          | 1             | C4000H          | 16K              |  |  |  |  |

|       |                        | 0        | 1                                                                               | 0          | 0             | C8000H          | 16K              |  |  |  |  |

|       |                        | 0        | 1                                                                               | 0          | 1             | CC000H          | 16K              |  |  |  |  |

|       |                        | 0        | 1                                                                               | 1          | 0             | D0000H          | 16K              |  |  |  |  |

|       |                        | 0        | 1                                                                               | 1          | 1             | D4000H          | 16K              |  |  |  |  |

|       |                        | 1        | 0                                                                               | 0          | 0             | D8000H          | 16K              |  |  |  |  |

|       |                        | 1        | 0                                                                               | 0          | 1             | DC000H          | 16K              |  |  |  |  |

|       |                        | 1        | 0                                                                               | 1          | 0             | C0000H          | 32K              |  |  |  |  |

|       |                        | 1        | 0                                                                               | 1          | 1             | C8000H          | 32K              |  |  |  |  |

|       |                        | 1        | 1                                                                               | 0          | 0             | D0000H          | 32K              |  |  |  |  |

|       |                        | 1        | 1                                                                               | 0          | 1             | D8000H          | 32K              |  |  |  |  |

|       |                        | 1        | 1                                                                               | 1          | 0             | C0000H          | 64K              |  |  |  |  |

|       |                        | 1        | 1                                                                               | 1          | 1             | D0000H          | 64K              |  |  |  |  |

|       |                        | These fo | our bits ca                                                                     | n be updat | ed by writi   | ng new values t | to this register |  |  |  |  |

| 4 - 5 |                        | Reserve  | d                                                                               |            |               |                 |                  |  |  |  |  |

| 6     | PnP                    | DM9008   | is in PnP                                                                       | state whe  | en this bit i | s set           |                  |  |  |  |  |

| 7     |                        | Reserve  | d                                                                               |            |               |                 |                  |  |  |  |  |

# Configuration Register D (CONFIG. D)

This register can be read or written at register 07H of ENC Page 3. All bits of this register are power-on low.

| 7      | 6 | 5 | 4       | 3    | 2    | 1    | 0    |

|--------|---|---|---------|------|------|------|------|

| EEMODE |   |   | CLK-REF | EECS | EECK | EEDO | EEDI |

| Bit  | Symbol  | Description                                                                                                                |

|------|---------|----------------------------------------------------------------------------------------------------------------------------|

| 0    | EEDI    | EEPROM DATA IN: This bit reflects the state of the DM9008 MD0 pin                                                          |

| 1    | EEDO    | EEPROM DATA OUT: When EEMODE is high, this bit reflects the state of the DM9008 MD1 pin                                    |

| 2    | EECK    | EEPROM CLOCK: When EEMODE is high, this bit reflects the state of the DM9008 MD2 pin                                       |

| 3    | EECS    | EEPROM CHIP SELECT: When EEMODE is high, this bit reflects the state of the DM9008 EECS pin                                |

| 4    | CLK-REF | When EEMODE is high, this bit is toggled every $12\mu s$                                                                   |

| 5, 6 |         | Reserved. Must be set to zero                                                                                              |

| 7    | EEMODE  | EEPROM MODE: If this bit is set high, the EEPROM can be programmed with the values of EECS, EECK and EEDO in this register |

# Interrupt Line Status Register

The logic value of DM9008's eight interrupt pins can be read in register 09H of ENC, page 2.

|       | 7       | 6                                                                 | 5     | 4     | 3       | 2    | 1    | 0    |  |

|-------|---------|-------------------------------------------------------------------|-------|-------|---------|------|------|------|--|

|       | IRQ15   | IRQ12                                                             | IRQ11 | IRQ10 | IRQ9    | IRQ5 | IRQ4 | IRQ3 |  |

| Bit   | Symbol  |                                                                   |       |       | Descrip | tion |      |      |  |

| 0 - 7 | IRQ3-15 | INTERRUPT LINE STATUS: The logic values of interrupt pins IRQ3-15 |       |       |         |      |      |      |  |

#### Interrupt Line Pull-Down Register

When any one of the eight bits in register 09H of ENC page 2 is set to one, the corresponding interrupt line will be pulled down to GND with a resistor whose value is approximately 1K. All bits of this register are power-on low.

| 7       | 6       | 5       | 4       | 3      | 2      | 1      | 0      |

|---------|---------|---------|---------|--------|--------|--------|--------|

| IRQPD15 | IRQPD12 | IRQPD11 | IRQPD10 | IRQPD9 | IRQPD5 | IRQPD4 | IRQPD3 |

| Bit   | Symbol    | Description                                                                                       |

|-------|-----------|---------------------------------------------------------------------------------------------------|

| 0 - 7 | IRQPD3-15 | INTERRUPT LINE PULL-DOWN: When one, enables the interrupt line to be pulled down with 1K resistor |

#### **Boot ROM Page Register**

The boot ROM page register can be read or written in register 0AH of ENC page 2. All bits of this register are power-on low.

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| XMA8 | XMA7 | XMA6 | XMA5 | XMA4 | XMA3 | XMA2 | XMA1 |

| Bit   | Symbol | Description                                                                                                                |

|-------|--------|----------------------------------------------------------------------------------------------------------------------------|

| 0 - 7 | XMA1-8 | BOOT ROM PAGE ADDRESS: When boot ROM is read by host, the value of this register will be indicated by MEMORY ADDRESS PA0-7 |

## Command Register (CR)

The Command Register is used to initiate transmissions, enable or disable Remote DMA operations, and select register pages. To issue a command, the microprocessor sets the corresponding bit(s) (RD2, RD1, RD0, TXP). Further commands may be overlapped, but with the following rules: (1) If a transmit command overlaps a remote DMA operation, bits RD0, RD1, and RD2 must be maintained for the remote DMA command when the TXP bit is set. Note that if a remote DMA command is re-issued when the transmit command is given, the DMA will be completed immediately if the remote byte count register has not been reinitialized. (2) If a remote DMA operation overlaps a transmission, RD0, RD1, and RD2 may be written with the desired values and a "0" may be written to the TXP bit. Writing a "0" to this bit has no effect. (3) A remote write DMA may not overlap a remote read operation or vice versa. Either of these operations must either be completed or be aborted before the other operation may start. Bits PS1, PS0, RD2 and STP may be set at any time.

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| PS1 | PS0 | RD2 | RD1 | RD0 | TXP | STA | STP |

| Bit            | Symbol            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|----------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| D0             | STP               | STOP: Software reset command. Takes the controller off-line, and no packets will be received or transmitted. Any reception or transmission in progress will continue to completion before the reset state is entered. To exit this state, the STP bit must be reset. The software reset is executed only when indicated by the RST bit in the ISR being set to a "1." STP powers up high                                                                                                             |  |  |  |  |  |

| D1             | STA               | Start mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| D2             | ТХР               | Transmit Packet: This bit must be set to initiate transmission of a packet. TXP is internally reset after the transmission is either completed or aborted. This bit should be set only after the Transmit Byte Count and Transmit Page Start registers have been programmed. TXP powers up low                                                                                                                                                                                                       |  |  |  |  |  |

| D3<br>D4<br>D5 | RD0<br>RD1<br>RD2 | Remote DMA Command: These three encoded bits control operation of the Remote DMA channel. RD2 can be set to abort any Remote DMA command in progress. The Remote Byte Count Registers should be cleared when a Remote DMA has been aborted. The Remote Start Addresses are not restored to the starting address if the Remote DMA is aborted. RD2 powers up high RD2 RD1 RD0<br>0 0 0 Not Allowed<br>0 0 1 Remote Read<br>0 1 0 Remote Write<br>0 1 1 Send Packet<br>1 X X Abort/Complete Remote DMA |  |  |  |  |  |

| D6<br>D7       | PS0<br>PS1        | Page Select: These two encoded bits select which register page is to be accessed with addresses SA0-3         PS1       PS0         0       0       Register Page 0         0       1       Register Page 1         1       0       Register Page 2         1       1       Register Page 3                                                                                                                                                                                                          |  |  |  |  |  |

# Data Configure Register (DCR)

This register is used to program the DM9008 for the 8 or 16-bit memory interface, select byte ordering in 16-bit applications, and establish FIFO thresholds. The DCR must be initialized prior to loading the Remote Byte Count Registers. LAS is set on power up.

| 7 | 6   | 5   | 4   | 3  | 2   | 1   | 0   |

|---|-----|-----|-----|----|-----|-----|-----|

|   | FT1 | FT0 | ARM | LS | LAS | BOS | WTS |

| Bit      | Symbol     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| D0       | WTS        | Word Transfer Select<br>0: Selects 8-bit DMA transfers<br>1: Selects 16-bit DMA transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| D1       | BOS        | Byte Order Select<br>0: MS byte placed on SD15-SD8 and LS byte on SD7-SD0 (32000, 8086)<br>1: MS byte placed on SD7-SD0 and LS byte on SD15-SD8 (68000)<br>Ignored when byte-wide DMA operation is chosen<br>Note: Byte Order Select mode is not supported in the current version of the DM9008, so<br>this bit should be cleared in the application                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| D2       | LAS        | Long Address Select<br>0: Dual 16-bit DMA mode<br>1: Single 32-bit DMA mode<br>Note: Single 32-bit DMA mode is not supported in the current version of the DM9008, so<br>this bit should be cleared in the application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| D3       | LS         | <ul> <li>Loopback Select</li> <li>0: Loopback mode selected. Bits D1, D2 of the TCR must also be programmed for<br/>Loopback mode selected</li> <li>1: Normal Operation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| D4       | ARM        | <ul> <li>Auto-initialize Remote</li> <li>0: Send Command not executed, all packets removed from Buffer Ring under program control</li> <li>1: Send Command executed, Remote DMA auto-initialized to remove packets from Buffer Ring</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| D5<br>D6 | FT0<br>FT1 | FIFO Threshold Select:       Encoded       FIFO threshold. During reception, the FIFO threshold indicates the number of bytes (or words) filled into the FIFO serially from the network before received data are written to the buffer RAM         Receive Thresholds       FT1       FT0       Word Wide       Byte Wide         0       0       1 Word       2 Bytes       0       1 2 Words       4 Bytes         1       0       4 Words       8 Bytes       1       6 Words       12 Bytes         During transmission, the FIFO threshold indicates the number of bytes (or words filled into the FIFO from the Local DMA before transmitted data are read from the buffer RAM. Thus, the transmission threshold is 16 bytes       1 bytes       16 bytes |  |  |  |  |

| D7       |            | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

# Transmit Configuration Register (TCR)

The transmit configuration register determines the actions of the transmitter section of the DM9008 during transmission of a packet on the network. LB1 and LB0 power up as 0.

| 7 | 6 | 5 | 4    | 3   | 2   | 1   | 0   |

|---|---|---|------|-----|-----|-----|-----|

|   |   |   | OFST | ATD | LB1 | LB0 | CRC |

| Bit      | Symbol     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| D0       | CRC        | Inhibit CRC<br>0: CRC appended by transmitter<br>1: CRC inhibited by transmitter                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| D1<br>D2 | LB0<br>LB1 | Encoded Loopback Control: These encoded configuration bits set the type of loopback that<br>is to be performed. Note that loopback in mode 2 sets the ENA in loopback mode and<br>that D3 of the DCR must be set to zero for loopback operation<br>LB1 LB0<br>Mode 0 0 0 Normal Operation<br>Mode 1 0 1 ENC moduleLoopback<br>Mode 2 1 0 ENA moduleLoopback<br>Mode 3 1 1 Loopback to Coax                                                                          |  |  |  |  |  |

| D3       | ATD        | <ul> <li>Auto Transmit Disable: This bit allows another station to disable the DM9008 transmitter by transmission of a particular multicast packet. The transmitter can be re-enabled by resetting this bit or by reception of a second particular multicast packet</li> <li>0: Normal Operation</li> <li>1: Reception of multicast address hashing to bit 62 disables transmitter; reception of multicast address hashing to bit 63 enables transmitter</li> </ul> |  |  |  |  |  |

| D4       | OFST       | <ul> <li>Collision Offset Enable: This bit modifies the backoff algorithm to allow propitiation of nodes</li> <li>0: Backoff Logic implements normal algorithm</li> <li>1: Forces Backoff algorithm modification to 0 to 2 <sup>min(3+n,10)</sup> slot times for first three collisions, then follows standard backoff. (For first three collisions, station has higher average backoff delay, resulting in a low priority mode.)</li> </ul>                        |  |  |  |  |  |

| D5       |            | Reserve must be set to zero                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| D6       |            | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| D7       |            | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

# Transmit Status Register (TSR)

This register records events that occur on the media during transmission of a packet. It is cleared when the next transmission is initiated by the host.

All bits remain low unless the event that corresponds to

a particular bit occurs during transmission. Each transmission should be followed by a read of this register. The contents of this register are not specified until after the first transmission.

|     | 7      | 6                         | 5                                                                                                                                                                                                                                                                                                                                                                                         | 4                            | 3            | 2                                | 1             | 0              |        |

|-----|--------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------|----------------------------------|---------------|----------------|--------|

|     | OWC    | CDH                       | FU                                                                                                                                                                                                                                                                                                                                                                                        | CRS                          | ABT          | COL                              |               | PTX            |        |

| Bit | Symbol |                           |                                                                                                                                                                                                                                                                                                                                                                                           |                              | Descri       | otion                            |               |                |        |

| D0  | ΡΤΧ    |                           | ansmitted: Ir<br>(ABT ="0", F                                                                                                                                                                                                                                                                                                                                                             |                              | smission wit | hout error (ne                   | o excessive   | colli-sions or | FIFO   |

| D1  |        | Reserved                  |                                                                                                                                                                                                                                                                                                                                                                                           |                              |              |                                  |               |                |        |

| D2  | COL    |                           |                                                                                                                                                                                                                                                                                                                                                                                           |                              |              | collided at lea<br>d in the Num  |               |                |        |

| D3  | ABT    |                           |                                                                                                                                                                                                                                                                                                                                                                                           |                              |              | oorted transn<br>ng original tra |               |                |        |

| D4  | CRS    | Carrier Se                | ense is moni                                                                                                                                                                                                                                                                                                                                                                              |                              | ne end of Pr | er is lost duri<br>eamble/Syncl  |               |                |        |

| D5  | FU     |                           |                                                                                                                                                                                                                                                                                                                                                                                           | ENC cannot<br>le packet will |              | to the bus be                    | efore the FIF | empties, this  | bit is |

| D6  | CDH    | packet wil<br>first 6.4µs | CD Heartbeat: Failure of the transceiver to transmit a collision signal after transmission of a packet will set this bit. The Collision Detect (CD) heartbeat signal must commence during the first $6.4\mu s$ of the interframe gap followinga transmission. In certain collisions, the CD heartbeat bit will be set even though the transceiver is not performing the CD heartbeat test |                              |              |                                  |               |                |        |

| D7  | OWC    |                           | Out of Window Collision: Indicates that a collision occurred after a slot time (51.2µs).<br>Transmissions are rescheduled as in normal collisions                                                                                                                                                                                                                                         |                              |              |                                  |               |                |        |

# **Receive Configuration Register (RCR)**

This register determines the operation of the NIC during reception of a packet, and is used to program what types of packets to accept.

| 7 | 7 | 6 | 5   | 4   | 3  | 2   | 1   | 0   |

|---|---|---|-----|-----|----|-----|-----|-----|

|   |   |   | MON | PRO | AM | ABP | ARP | SEP |

| Bit     | Symbol       | Description                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|---------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| D0      | SEP          | Save Errored Packets<br>0: Packets with receive errors are rejected<br>1: Packets with receive errors are accepted. Receive errors are CRC and Frame<br>Alignment errors                                                                                                                                                                                         |  |  |  |  |  |  |

| D1      | ARP          | ccept Runt Packets<br>Packets with fewer than 64 bytes rejected<br>Packets with fewer than 64 bytes accepted                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| D2      | ABP          | Accept Broadcast<br>0: Packets with all 1's broadcast destination address rejected<br>1: Packets with all 1's broadcast destination address accepted                                                                                                                                                                                                             |  |  |  |  |  |  |

| D3      | AM           | Accept Multicast<br>0: Packets with multicast destination address not checked<br>1: Packets with multicast destination address checked                                                                                                                                                                                                                           |  |  |  |  |  |  |

| D4      | PRO          | <ul> <li>Promiscuous Physical</li> <li>0: Physical address of node must match the station address programmed in PARO-PAR5 (physical address checked)</li> <li>1: All packets with physical address accepted (physical address not checked)</li> </ul>                                                                                                            |  |  |  |  |  |  |

| D5      | MON          | <ul> <li>Monitor Mode: Enables the receiver to check addresses and CRC on incoming packets without buffering to memory. The Missed Packet Tally counter will be incremented for each recognized packet</li> <li>0: Packets buffered to memory</li> <li>1: Packets checked for address match, good CRC and Frame Alignment, but not buffered to memory</li> </ul> |  |  |  |  |  |  |