#### **Technical Reference Manual**

# BA-81C15 HIGH PERFORMANCE PCI TO SCSI HOST ADAPTER CHIP

#### **Revision History**

| Revision | Change Activity                           | Date    |

|----------|-------------------------------------------|---------|

| A        | Release                                   | 1/31/96 |

| В        | Changes reflect BA-81C15 Rev. F and above | 3/22/96 |

#### Copyright

© Copyright 1996 BusLogic Inc. All rights reserved.

BusLogic Inc makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. BusLogic is not liable for any errors contained herein or incidental or consequential damages in connection with furnishing, performance, or use of this material.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced, or translated to another language without prior written consent of BusLogic Inc.

#### **Trademarks**

Company and product names are trademarks or registered trademarks of their respective companies.

## **Table of Contents**

| Chapter 1: Functional Definition                 |                 |

|--------------------------------------------------|-----------------|

| About This Chapter                               | 1-1             |

| Key Features                                     |                 |

| Overview                                         | 1-2             |

| Initiator/Disconnected Modes                     | 1-5             |

| Arbitration, Selection, and Re-Selection Control |                 |

| SCSI Bus Phase Changes and Data Transfer         |                 |

| Synchronous Transfer Support                     |                 |

| 32-Byte SCSI FIFO                                |                 |

| Timeout                                          | 1-4             |

| SCSI Three-State Drivers                         | 1-4             |

| Parity Logic                                     | 1-5             |

| Automation Logic                                 | 1-5             |

| DMA Interface                                    | 1-5             |

| BIOS PROM Interface                              | 1- <del>(</del> |

| Automated Scatter/Gather Handling                | 1- <del>6</del> |

| SEEPROM Download at Power On Reset               | 1-7             |

| Chantar 2: Din Definitions                       |                 |

| Chapter 2: Pin Definitions                       |                 |

| About This Chapter                               |                 |

| PCI Interface Pins                               |                 |

| External Memory Interface Pins                   |                 |

| SCSI Interface Pins                              | 2- <i>e</i>     |

| Miscellaneous Pins                               |                 |

| Power/Ground Pins                                | 2-7             |

| Chapter 3: Address Space                         |                 |

| About This Chapter                               |                 |

| About This Chapter                               | 3-1             |

| Chapter 4: Register Reset Condition Description  |                 |

| About This Chapter                               | 1_1             |

| PCI Configuration Space Register Reset Condition |                 |

| Host Register File Reset Condition               |                 |

| SCSI Block Register Reset Condition              |                 |

| 0                                                | 1               |

| Chapter 5: Register Summary                      |                 |

| About This Chapter                               | 5-1             |

| PCI Configuration Space                          |                 |

| Host Register File                               | 5- <del>6</del> |

| SCSI Register File                               | 5-10            |

| Scatter/Gather Instruction RAM                   | 5-14            |

| SCSI Automation RAM                              |                 |

| Chapter 6: Register Definition                       |             |

|------------------------------------------------------|-------------|

| About This Chapter                                   | 6-1         |

| PCI Configuration Space                              | 6-2         |

| Host Register File                                   | <b>6-</b> 5 |

| SCSI Register File                                   | 6-14        |

| Chapter 7: Automation Instructions                   |             |

| About This Chapter                                   | 7 1         |

| No-Operation/Delay Instructions                      |             |

| No Operation/Delay Instructions                      |             |

| Compare Instructions                                 |             |

| Compare Register with Instruction Data               |             |

| Compare Register with Register                       |             |

| Branch Instructions                                  |             |

| Compare SCSI Phase and Branch Equal                  |             |

|                                                      |             |

| Compare SCSI Phase and Branch Not Equal              |             |

| Branch                                               |             |

| Test Condition and Branch                            |             |

| Move Instructions                                    |             |

| Match SCSI Phase and Move Instruction Data           |             |

| Move Instruction Data to Register                    |             |

| Move Register to Register                            |             |

| Logic Instructions                                   |             |

| Logical AND Register with Instruction Data           |             |

| Logical AND Register with Instruction Data and Store |             |

| Logical OR Register with Instruction Data            |             |

| Logical OR Register with Instruction Data and Store  |             |

| Modify Instructions                                  |             |

| Store to SCSI Register                               |             |

| Reset ATN on REQ                                     |             |

| Stop and Set Interrupt                               | 7-11        |

| Chapter 8: Electrical Information                    |             |

| About This Chapter                                   |             |

| Absolute Maximum Ratings                             |             |

| Operating Test Conditions                            |             |

| DC Parameters                                        |             |

| DC Specifications for PCI                            |             |

| SCSI                                                 |             |

| Memory Port                                          |             |

| Clock Timing                                         |             |

| OSCI Table                                           |             |

| PCI Timing                                           |             |

| Timing Parameters                                    |             |

| Wave Forms                                           | 8-8         |

| Appendix A: Package Description                      |             |

| Glossary                                             |             |

| BusLogic Customer Service                            |             |

| · • · · · · · · · · · · · · · · · · · ·              |             |

# **List of Figures**

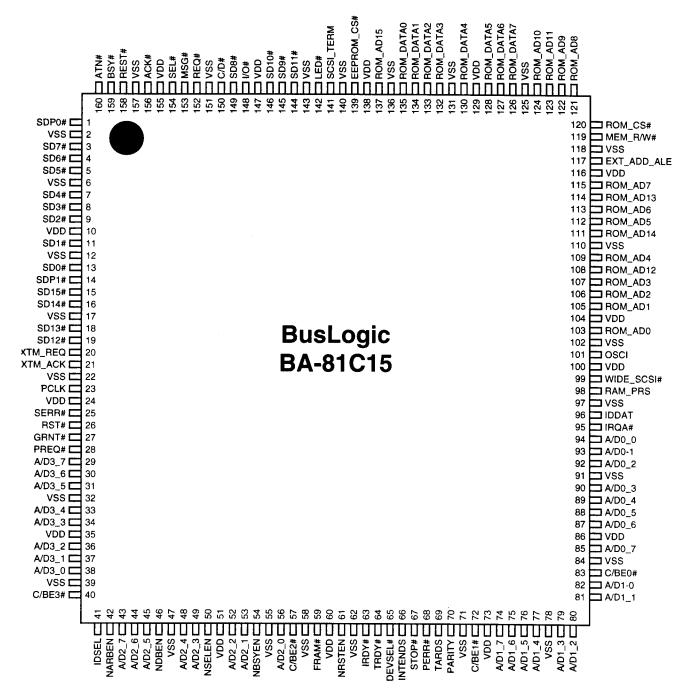

| Figure 2-1. BA-81C15 Pin Layout                         | 2-3  |

|---------------------------------------------------------|------|

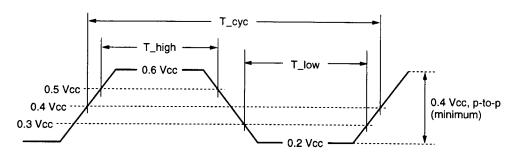

| Figure 8-1. 3.3 V Clock Waveform                        |      |

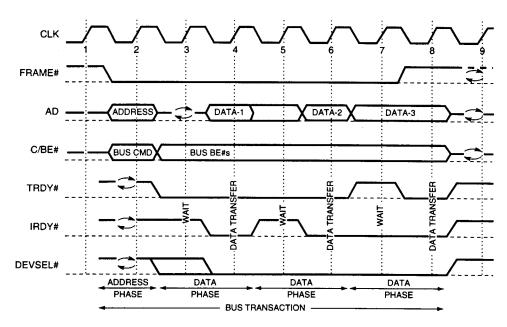

| Figure 8-2. Basic Read Operation                        |      |

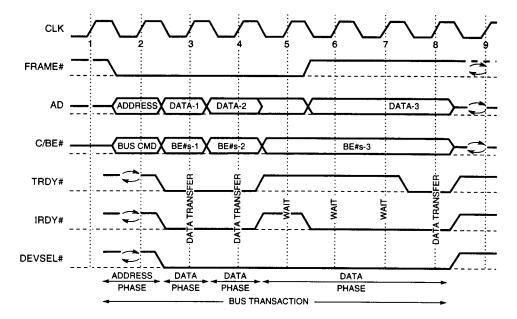

| Figure 8-3. Basic Write Operation                       |      |

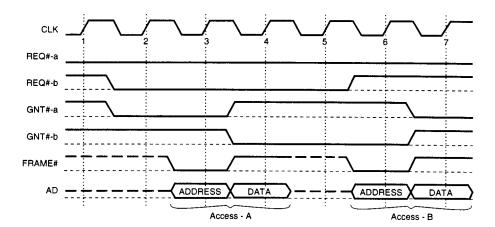

| Figure 8-4. Basic Arbitration                           |      |

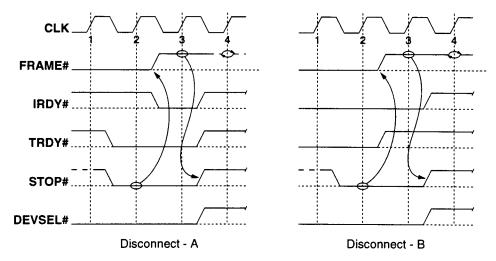

| Figure 8-5. Disconnect with Data                        | 8-8  |

| Figure 8-6. Retry                                       |      |

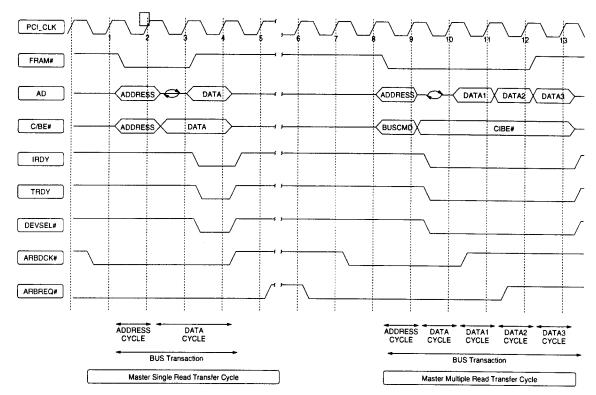

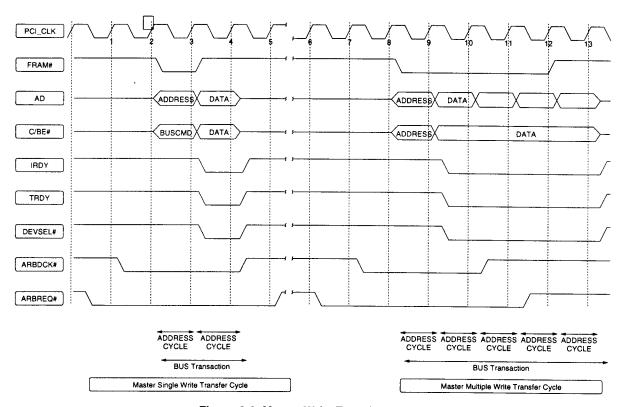

| Figure 8-7. Master Read Transfer Cycle                  | 8-9  |

| Figure 8-8. Master Write Transfer Cycle                 |      |

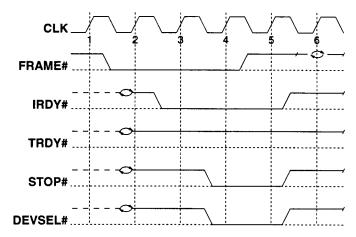

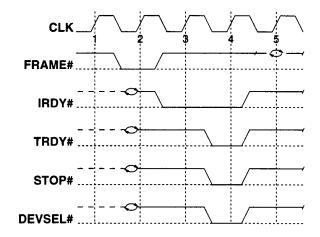

| Figure 8-9. Master Completion Termination               | 8-10 |

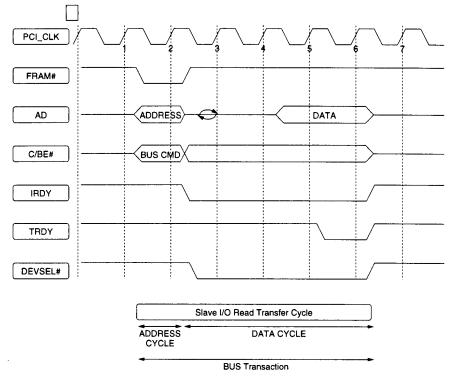

| Figure 8-10. Slave I/O Read Transfer Cycle              | 8-10 |

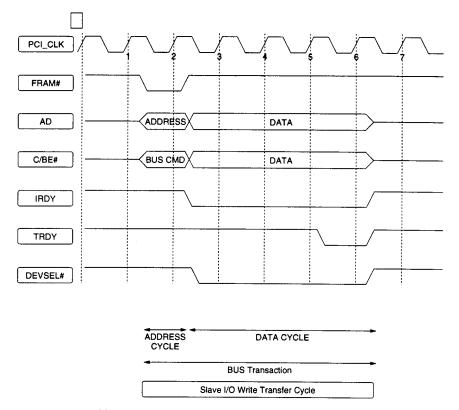

| Figure 8-11. Slave I/O Write Transfer Cycle             |      |

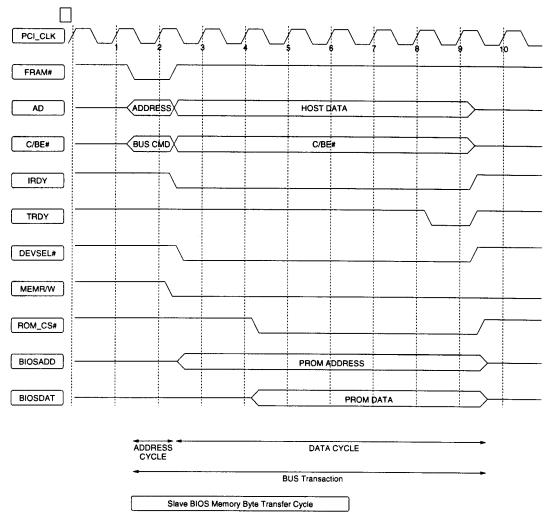

| Figure 8-12. Slave BIOS Memory Byte Transfer Cycle      |      |

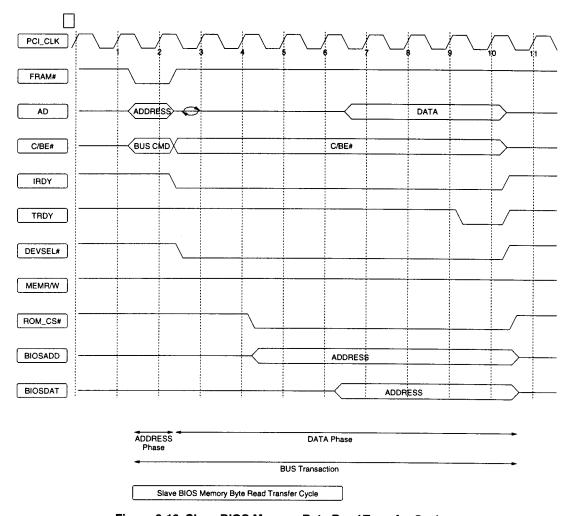

| Figure 8-13. Slave BIOS Memory Byte Read Transfer Cycle |      |

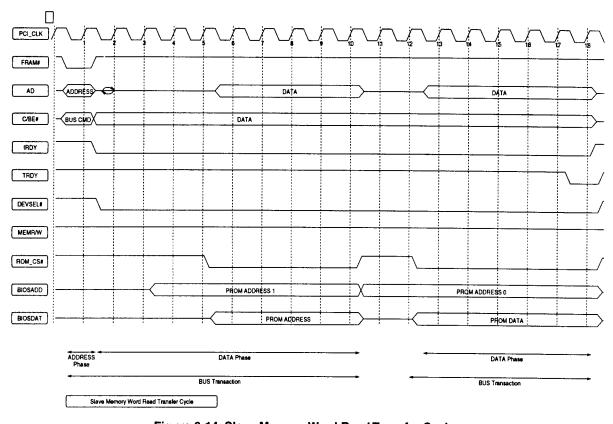

| Figure 8-14. Slave Memory Word Read Transfer Cycle      |      |

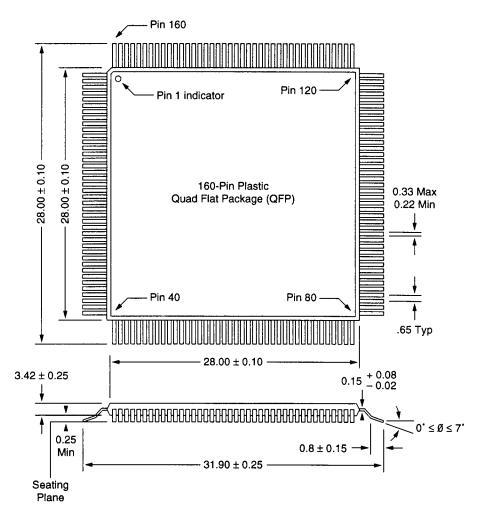

| Figure A-1. Package Description                         |      |

## **List of Tables**

| Table 1-1. Format of the SEEPROM Space                     | 1-7 |

|------------------------------------------------------------|-----|

| Table 2-1. PCI Interface Pins                              | 2-4 |

| Table 2-2. External Memory Interface Pins                  | 2-5 |

| Table 2-3. SCSI Interface Pins                             |     |

| Table 2-4. Miscellaneous Pins                              |     |

| Table 2-5. Power/Ground Pins                               | 2-7 |

| Table 8-1. DC Specifications for 5 V Signaling             |     |

| Table 8-2. SCSI Signals—SD(15-0)/, SDPO/, REQ/, MSG/, I/O, |     |

| C/D, ATN/ ACK/, BSY/, SEL/, RST/, SDP1/                    | 8-3 |

| Table 8-3. Clock Specifications                            | 8-4 |

| Table 8-5. 5 V and 3.3 V Timing Parameters                 |     |

#### **Functional Definition**

# **About This Chapter**

Read this chapter to find out

- Features of the BA-81C15 PCI host adapter chip

- A general overview of the BA-81C15 to SCSI host adapter chip

#### **Functional Definition**

#### **Key Features**

- 10 MB/sec FAST SCSI synchronous 8-bit data transfers

- 20 MB/sec FAST20 SCSI synchronous 8-bit data transfers

- 20 MB/sec FAST/WIDE SCSI synchronous 16-bit data transfers

- 40 MB/sec FAST20/WIDE SCSI synchronous 16-bit data transfers

- 14 MB/sec SCSI asynchronous 16-bit data transfers

- 132 MB/sec PCI host bus transfers

- 32-byte SCSI FIFO

- 128-byte host FIFO

- 128-byte program RAM for SCSI automation

- 128-byte host automation RAM

- Intelligent initiator control reduces host processor overhead

- Connects to up to fifteen SCSI peripherals in wide mode

- Differential SCSI support

- Support for SCAM Level 2

- Support for PCI Sub-System ID

- Low power CMOS technology

#### **Overview**

The BA-81C15 chip is an integrated PCI to SCSI host adapter chip. The BA-81C15 has been designed to perform 20 MB/sec Fast20 SCSI data transfers in 8-bit mode or 40 MB/sec Fast/Wide SCSI data transfers in 16-bit mode with an UltraSCSI bus. Using its low-level operating mode and automation commands, the BA-81C15 is able to handle normal SCSI protocol with a minimum of processor intervention. The low-level operations quickly hand operations directly to the SCSI bus under the control of the host processor. The user can also program commands or instructions to the automation RAM, which enables the BA-81C15 SCSI to handle the SCSI protocol. The program automation RAM can control most initiator operations.

Host automation can handle up to sixteen commands, which include address and count for a Scatter/Gather list. This RAM, which is 32x32 bits, could be shared with the onboard BIOS<sup>1</sup>. On the host bus, burst transfers can be handled at up to the maximum PCI transfer rate. The host FIFO will operate in 8-, 16- or 32-bit modes to or from the host side and in 8- or 16-bit modes to or from the SCSI side.

<sup>&</sup>lt;sup>1</sup> There is a 32x8 stack that the BIOS can use without having to share the Scatter/Gather RAM.

#### Initiator/Disconnected Modes

When the BA-81C15 completes an "arbitrate and select a target" or if it successfully responds to "re-selection as an initiator," it automatically puts itself into Initiator mode. These operations are enabled by means of a bit in SCSI Control 0 Register 45h, R/W. When the BA-81C15 is not in Initiator mode, it is said to be in Disconnected mode (even if the SCSI bus is not in Bus-Free phase; another connection involving the BA-81C15 may be ongoing). The Initiator Mode Bit (R/W) is available in Reset Register 47h Bit 7, R/W.

#### **Arbitration, Selection, and Re-Selection Control**

The BA-81C15 can automatically perform all of the functions to arbitrate, select, or be re-selected. When the BA-81C15 is enabled to perform the Select Target operation (by those bits in SCSI Control 0 Register 45h), it will wait for bus free, then arbitrate for the SCSI bus (using the ID specified in the Arbitration ID Register 52h [3:0]). If the BA-81C15 wins arbitration, it will then select the appropriate Target (specified in the SCSI Select ID Register 53h [3:0]).

In addition, if the SCSI Interface Control Register 45h Bit 2 is set, the BA-81C15 will respond to re-selection by another device on the SCSI bus. The successful completion of this operation will cause the ReSel Comp Bit (Interrupt Status Register 42h Bit 3) to be set, which can result in the external interrupt signal asserting (if that particular interrupt source is enabled). The SCSI ID of the device re-selecting the BA-81C15 will be stored into the Selected ID (Reg 53h [7:4]). The BA-81C15's current SCSI ID will be stored in Current ID (Reg 52h [7:4]). This is useful if multiple bits are set in the Wait for Self ID Registers (Reg 50h, 51h [7:0]).

## SCSI Bus Phase Changes and Data Transfer

An Information phase is defined by the state of the C/D, MSG, and I/O signals (the "SCSI bus phase control signals set by the target") only if the REQ signal is asserted. SCSI has several bus phases to handle the different types of information transfers between the Initiator and the Target.

While in Initiator mode, the BA-81C15 will not automatically assert the ACK signal to handshake or transfer data on the SCSI bus if a "phase-mismatch" occurs. A phase-mismatch is defined as the assertion of REQ (by the Target) when the SCSI bus phase control signals (also driven by the Target) do not match the corresponding values in SCSI Signal Register 44h [2:0]. If a phase-mismatch occurs, a SCSI Phase Change Status and Interrupt (if enabled) is generated to the host CPU, and the low-level driver must take appropriate action. Once enabled, the BA-81C15 will continue to transfer data (and keep generating ACK pulses) until a new phasemismatch occurs or the SCSI bus reset occurs. Data will continue to transfer even if the SCSI block transfer counter is zero; therefore the transfer counter is used to keep track of large blocks of data when the BA-81C15 is in Initiator mode and not to control the operation. In Initiator mode, the transfer counter is decremented on reads from the FIFO so that the transfer counter can be loaded after the SCSI transfer has started on reads; therefore, on writes, the transfer counter will reflect the amount of data the Target has accepted. The data transfer is controlled by the Bus-Master transfer counter.

#### Synchronous Transfer Support

Per SCSI specification, the only SCSI bus phases that can utilize synchronous transfers are the two data phases (Data In and Data Out). The BA-81C15 automatically detects when the current bus phase is equal to the Data In phase and receives synchronous data without the need to match the SCSI phase. The BA-81C15 also automatically enables the SCSI FIFO port. The Data Out phase is started by matching the phase. The target REQ(s) are stored by the offset counter prior to the phase being matched so that the offset is preserved.

Most of the time the synchronous control logic is automatically set up at the time the Initiator is connected to the SCSI Target. The Selected ID is stored at the time of selection or re-selection. The Selected ID is used to point to one of sixteen Target Registers. The Target Registers store the sync rate, the SCSI bus width, and the maximum sync offset. These are assigned by the driver during sync negotiation. In this way the SCSI Sync Registers are addressed by the Selected ID, which is loaded every time a selection or re-selection occurs.

Whenever the BA-81C15 is transferring data in a non-data information transfer phase, it uses async transfer mode, regardless of the values in the SCSI Synchronous Control Register.

#### 32-Byte SCSI FIFO

The BA-81C15 has two 16x9 bit FIFOs which can be configured for either 8-bit or 16-bit mode, depending on the width of the SCSI device. Two channels can simultaneously access the FIFO: a read channel and a write channel. The SCSI FIFO is used mostly for data, but other information can go through it. It has a dual port memory, separate read and write address counters, and a synchronous up-down counter which keeps track of the status of the SCSI FIFOs.

#### **Timeout**

The BA-81C15 provides a "load and forget" timeout interrupt-generation mechanism. This mechanism is built around a 20-bit counter clocked at approximately 2.5 MHz, depending on the OCS frequency and the value in SCSI CNTL (Register 6Dh [2:0]). There is an 8-bit Compare (Timeout Value Register 6Ch [7:0]) and a general purpose "START\_TIMEOUT" bit (Port Control Register 46h Bit 0). The timeout is used automatically during selection. The magnitude of the timeout can be adjusted using Reg 4Eh Bit 7. This bit allows the use of much shorter timeout conditions, such as those required by SCAM. Manual use of the timer is covered in Chapter 6, Register Definition.

#### **SCSI Three-State Drivers**

The BA-81C15's SCSI buffers are programmable to be either open collector (open drain) or three-state. The open collector buffers are the standard 48mA drivers. (Note that SCSI-3 will require active terminations.)

Note: For applications needing higher speeds, there is the option to add active deassertion (see bit "ENABLE Active Deassertion" in SCSI CLK Control, 65h, Bit 4). The BA-81C15 is equipped with an active pull-up consisting of an N-channel transistor to Vdd. This weak N-channel device will not cause a problem with the operation of the SCSI bus when the BA-81C15 is powered down. The weak N-channel will not overdrive the standard or active terminators, causing term power problems. The weak N-channel will allow the SCSI device to be hot-plugged as long as the bus is quiescent.

#### **Parity Logic**

The BA-81C15 can generate or check parity. In addition, there is an option to invert parity information on *data being written to the FIFO* (from any source). There is one bit of parity per byte of data. Parity errors can optionally generate interrupts.

#### **Automation Logic**

The automation logic is used to reduce the number of interrupts. There is an automation instruction RAM (64x 6 bits) which can be programmed to hold normal messages, commands, check the SCSI phases, and control signals automatically responding to the Target. The method used is first to decide on the sequence needed. Program the automation RAM, enable the automation logic (using the desired start condition in Regs 64–67h, R/W), and then enable the Select Target (Reg 45h Bit 6, R/W) usually with ATN (Reg 45h Bit 4, R/W). After the BA-81C15 has gained access to the target and once the starting condition is met, the automation logic will begin executing instructions. These instructions include waiting for a particular phase, transferring a message or status byte into one of the general purpose registers (Regs 68h-6Bh), generating interrupts and the like.

The automation logic will halt once it encounters a Stop and Set Interrupt command (SSI) (Reg 43h [0:4]) or when a phase is encountered that has not been anticipated (Reg 42h Bit 6). The automation program counter will contain the offset into the automation RAM where the automation stopped execution. The automation RAM will be loaded at initialization time with a generic script or map and then can be modified for each specific command. This allows about 85 percent of the map to remain constant and only requires such commands as the CDB or the identify message to be loaded for each operation.

Multiple starting conditions can be enabled simultaneously, but only one of these can start the automation at a time. Once one condition does start the automation, the other starting condition will remain active and will restart the automation once it has stopped and the condition is met.

Automation is covered in detail in Chapter 7.

#### **DMA** Interface

The DMA interface transfers 8 -bit data internal to the BA-81C15 between the PCI block and the SCSI block. In the DMA mode the SCSI block asserts the DMA\_REQ signal and the PCI block receives it. The SCSI block expects to send/receive data when the DMA\_ACK signal is asserted by the PCI block.

#### **BIOS PROM Interface**

The BA-81C15 requires a BIOS PROM to aid the operating system in configuring and using the I/O card. The code contained within the BIOS PROM is executed by the operating system to initialize the BA-81C15 and the I/O card, and to inform the operating system of the I/O card's presence. It may also provide the interface routines which communicate between an I/O driver and the I/O card (BA-81C15). It should be noted that when the BIOS PROM interface is 8 data bits wide, any code run directly from this PROM will execute slowly. The BIOS is read 4 bytes at a time and then given to the PCI interface in 32-bit format. For higher performance systems, the BIOS code should be copied into and executed from system RAM.

The method used to address the BIOS PROM is a 14-bit memory address bus and an 8-bit data bus, plus a ROM chip select. There is an Address Bit 15 provided under driver control to allow 64K ROM space.

#### **Automated Scatter/Gather Handling**

The BA-81C15 provides the ability to handle up to sixteen Scatter/Gather 8-byte segments at one time. This is accomplished by using the 128 bytes of Scatter/Gather RAM (SGRAM). The SGRAM is broken up into sixteen 8-byte chunks or segments and are numbered 0–15. Each segment is written into the SGRAM using 32-bit accesses. Once this SGRAM has been initialized, the starting and ending segment numbers, or pointers, are written into Reg 28h. This register tells the BA-81C15 where to start and end processing of the Scatter/Gather segments. Finally, Bit 0 of Reg 29h is enabled and the Scatter/Gather operation commences. The first 8-byte packet is copied into Scatter/Gather Instruction registers (Transfer Command Register 1Bh, Count Register 1Ah~18h, and Host Address 1Fh~1Ch), which start the transfer of the first Scatter/Gather elements data. The BA-81C15 allows the flexibility of selectively generating interrupts at the completion of each Scatter/Gather element by setting Bit 7 of the Transfer Command Register 1Bh. This way, the interrupt can be inhibited on all Scatter/Gather elements, except for the last, when the entire list has been processed.

#### **SEEPROM Download at Power On Reset**

The BA-81C15 supports PCI Configuration at power on reset by downloading values from the SEEPROM. The following table shows a description of the register, the PCI register address, and the SEEPROM address for each of the values which are loaded:

Table 1-1. Format of the SEEPROM Space

| Description                 | PCI Configuration Register                                                                                    | SEEPROM Address                    |

|-----------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------|

| Sub-sys Vendor ID:          | Reg. 0x2C-2D                                                                                                  | Word Address 0x28                  |

| Sub-sys Device ID:          | Reg. 0x2E-2F                                                                                                  | Word Address 0x29                  |

| Configuration Key:          | N/A                                                                                                           | Word Address 0x2A (value = 0x424C) |

| Interrupt Pin:<br>BIOS Size | Reg.0x3D bits (2-0) If bit 7- is cleared 32KB BIOS is used or if bit 7- is set then 64KB BIOS is used at POR. | Word Address 0x2B (low byte)       |

| Available: bits 15-8        |                                                                                                               | Word Address 0x2B (hi byte)        |

| Min Grant                   | Reg. 0x3E                                                                                                     | Word Address 0x2C (low byte)       |

| Max Latency                 | Reg. 0x3F                                                                                                     | Word Address 0x2C (hi byte)        |

| Card Bus CIS Pointer:       | Reg. 0x28-29                                                                                                  | Word Address 0x2D                  |

| Card Bus CIS Pointer:       | Reg. 0x2A-2B                                                                                                  | Word Address 0x2E                  |

The Sub-system ID will always be loaded into the appropriate registers at power-up. In addition, if the Configuration Key contains the proper value ("BL"), then the remaining registers will be loaded with the values stored in the SEEPROM. The Configuration Key has been added to prevent accidental loading of critical registers in the event a part is installed on a board containing a SEEPROM with old data. If the Configuration Key does not match, then the power on reset values inside the chip would be used.

The BIOS Size Register is one bit (bit 7), of Word Address 0x2B. FlashPoint currently requests a 32K ROM space and in the future, we may need to request 64K. If the byte in the SEEPROM contains 0x00, then ROM address bit 15 is writable and PCI Configuration will assign 32K. If the SEEPROM contains 0x8X, then bit 15 of the ROM address is not writable and PCI Configuration will assign 64K. The values of the SEEPROM register will not affect bit 2 of the Feature Ctrl (Reg. 0x29) BIOS SHADOW (0 = 32K, 1 = 64K), but in the case of 64K it will have no effect.

The Minimum Grant and Maximum Latency, Registers 3Eh, and 3Fh are both preset with 08h and can be downloaded with values from the SEEPROM. The values do not affect any logic in the BA-81C15 and they are used by the system in optimizing the PCI performance for the BA-81C15.

The Card Bus CIS Pointer, Register 28h-2Bh are preset to 00h and if the Configuration Key is correct, they are donwloaded from the SEEPROM. The Card Bus CIS Pointer is part of Card Information Structure. Refer to the PCMCIA v2.10 specification for details. It can be used to communicate an address to the BIOS or Software Driver as to the address of any code or parameter lists during initialization.

## **Pin Definitions**

# **About This Chapter**

Read this chapter to find out

- A summary of the pin pad type and signal assignment

- Pin layout of the BA-81C15

#### **Pin Definitions**

BA-81C15 pins are described here in tables listing the name (or symbol), number, type, and funtion. In these tables, the following abbreviations are used:

I/O - Input and output pinI - Input pin only

O - Output pin only; push-pull driver

TS - Three-state output pin OC - Open collector output pin

In addition, a diagram of the BA-81C15 pin layout is presented in Figure 2-1.

Figure 2-1. BA-81C15 Pin Layout

## **PCI Interface Pins**

Table 2-1. PCI Interface Pins

| Symbol                | Pin<br>Number                 | 1/0 | Function                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------|-------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCLK                  | 23                            | ı   | PCI CLK: Used to drive host logic.                                                                                                                                                                                                                                                                                                                                     |

| IDSEL                 | 41                            | l   | <b>Initialization Device Select:</b> Used as a chip select during configuration read and write transactions.                                                                                                                                                                                                                                                           |

| GRNT#                 | 27                            | ı   | <b>GRANT#:</b> GRNT as designated in the PCI Specification. This active low input from the PCI arbitration logic indicates that the master is granted the bus.                                                                                                                                                                                                         |

| PREQ#                 | 28                            | 0   | PCI Request: PREQ# indicates to the arbiter that this device desires use of the bus.                                                                                                                                                                                                                                                                                   |

| DEVSEL#               | 65                            | 1/0 | <b>PCI Device Select:</b> DEVSEL# is used as a chip select during configuration read and write transactions.                                                                                                                                                                                                                                                           |

| FRAME#                | 59                            | I/O | PCI Frame: FRAME# starts the PCI bus cycle.                                                                                                                                                                                                                                                                                                                            |

| STOP#                 | 67                            | 1/0 | PCI Stop: STOP# stops the PCI bus cycle.                                                                                                                                                                                                                                                                                                                               |

| IRDY#                 | 63                            | I/O | Initiator Ready#: IRDY# signal as designated in the PCI Specification.                                                                                                                                                                                                                                                                                                 |

| TRDY#                 | 64                            | 1/0 | Target Ready#: TRDY# signal as designated in the PCI Specification.                                                                                                                                                                                                                                                                                                    |

| PAR                   | 70                            | I/O | Parity Error*: PERR* signal as designated in the PCI Specification.                                                                                                                                                                                                                                                                                                    |

| PERR#                 | 68                            | 1/0 | Parity Error#: PERR# signal as designated in the PCI Specification.                                                                                                                                                                                                                                                                                                    |

| SERR#                 | 25                            | I/O | System Error#: SERR# signal as designated in the PCI Specification.                                                                                                                                                                                                                                                                                                    |

| IRQA#<br>(16mA)       | 95                            | TS  | Interrupt A#: IRAQ# signal as designated in the PCI Specification.                                                                                                                                                                                                                                                                                                     |

| A/D3 [7:0]<br>(20 mA) | 29-31,<br>33,34,<br>36-38     | I/O | Host Address/Data Byte 3 [7:0]: Bidirectional active high host multiplexed address and data bus.                                                                                                                                                                                                                                                                       |

| A/D2 [7:0]<br>(24mA)  | 43-45,<br>48,49,<br>52-53, 56 | 1/0 | Host Address/Data Byte 2 [7:0]: Bidirectional active high host multiplexed address and data bus.                                                                                                                                                                                                                                                                       |

| A/D1 [7:0]<br>(24mA)  | 74-77,<br>79-82               | I/O | Host Address/Data Byte 1 [7:0]: Bidirectional active high host multiplexed address and data bus.                                                                                                                                                                                                                                                                       |

| A/D0 [7:0]<br>(24mA)  | 85,<br>87-90,<br>92-94        | I/O | Host Address/Data Byte 0 [7:0]: Bidirectional active high host multiplexed address and data bus.                                                                                                                                                                                                                                                                       |

| C/BE [3:0]<br>(24mA)  | 40,57,<br>72,83               | I/O | Command/Byte Enables [3:0]: These determine the data paths that will be used by the current cycle of the PCI bus.                                                                                                                                                                                                                                                      |

| RST#                  | 26                            | İ   | <b>Reset#:</b> This active <i>low</i> input signal resets the BA-81C15. It puts the BA-81C15 into a power reset condition with all controllers and registers in the reset condition. The condition of resisters after reset is found in Chapter 5, Register Summary. This signal must be asserted for a minimum of two clocks after the Vdd pins have reached Vdd-min. |

# **External Memory Interface Pins**

Table 2-2. External Memory Interface Pins

| Symbol            | Pin<br>Number                                                                                      | VO  | Function                                                                                                                                                                                               |

|-------------------|----------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROM_AD<br>[15:0]  | 137, 111,<br>114, 108,<br>123, 124,<br>122, 121,<br>115, 113,<br>112, 109,<br>107, 106<br>105, 103 | I/O | ROM Address [15:0]: BIOS and external RAM address for BA-81C15 board product. BIOS is assumed to be fixed 32K x 8 EPROM or Flash. BIOS Shadow Bit (Reg 29h Bit 2) is used to address 64K x 8 memories. |

| ROM_DATA<br>[7:0] | 126-128,<br>130,<br>132-135                                                                        | 1/0 | ROM Data [7:0]: BIOS and external RAM data for BA-81C15 board product.                                                                                                                                 |

| ROM_CS#           | 120                                                                                                | TS  | ROM Chip Select: Chip Select for the BIOS ROM.                                                                                                                                                         |

| MEM_R/W#          | 119                                                                                                | TS  | <b>Memory Read/Write#:</b> Signal which determines whether the memory is read or written. Active high for Reads and active low for Writes.                                                             |

| WIDE#             | 99                                                                                                 | I   | Wide SCSI Bus: Used as strapping pin for narrow/wide SCSI applications.                                                                                                                                |

| RAM_PRS           | 98                                                                                                 | 1   | RAM_PRS: User Defined Input, connected to Feature Control Register, 29h, bit 5.                                                                                                                        |

| IDDAT             | 96                                                                                                 | I/O | <b>ID of the Board:</b> This value is used for Plug and Play and is shifted in at power on reset from external logic.                                                                                  |

| TARDS             | 69                                                                                                 | 0   | TARDS: Used as SCSI differential control signal indicating Target mode.                                                                                                                                |

| INTENDS           | 66                                                                                                 | 0   | INTENDS: Used as SCSI differential control signal indicating Initiator mode.                                                                                                                           |

| NRSTEN            | 61                                                                                                 | 0   | NRSTEN: Used as SCSI differential control signal indicating NRST is asserted.                                                                                                                          |

| NBSYEN            | 54                                                                                                 | 0   | NBSYEN: Used as SCSI differential control signal indicating NBSY is asserted                                                                                                                           |

| NSELEN            | 50                                                                                                 | 0   | NSELEN: Used as SCSI differential control signal indicating NSEL is asserted.                                                                                                                          |

| NDBEN             | 46                                                                                                 | 0   | NDBEN: Used as SCSI differential control signal indicating output data to bus.                                                                                                                         |

| NARBEN            | 42                                                                                                 | 0   | NARBEN: Used as SCSI differential control signal indicating arbitrate in process.                                                                                                                      |

| SCSI_TERM         | 141                                                                                                | TS  | SCSI Termination: Signal which can be used to enable the SCSI Termination under program control.                                                                                                       |

| EEPROM_CS         | 139                                                                                                | TS  | <b>EEPROM Chip Select:</b> Chip Select to control the EEPROM. The other pins necessary are multiplexed with the EPROM and RAM.                                                                         |

| LED#              | 142                                                                                                | ОС  | <b>LED:</b> LED is used to drive the LED connector, sending Device Select information to the front panel. The LED will be active when the SCSI Busy signal is active.                                  |

| #EXTM_ACK         | 21                                                                                                 | l   | <b>External Memory Acknowledge:</b> This signal is a general purpose input (Reg 22h Bit 7).                                                                                                            |

| #EXTM_REQ         | 20                                                                                                 | TS  | External Memory Request: This signal is a general purpose output (Reg 22h Bit 6).                                                                                                                      |

# **SCSI Interface Pins**

Table 2-3. SCSI Interface Pins

| Symbol              | Pin<br>Number                       | VO              | Function                                                                                                                                                                                                                                                                                                                                                            |

|---------------------|-------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BSY#<br>(48mA)      | 159                                 | I/O<br>OC       | <b>Busy#:</b> The SCSI Busy signal. Indicates that the SCSI bus is in use, and is also used to gain control of the bus. This signal does not have a programmable active internal pull-up. The input is Schmitt triggers input with nominal hysteresis of 400mV.                                                                                                     |

| SEL#<br>(48mA)      | 154                                 | I/O<br>OC       | <b>Select#:</b> The SCSI Select Device signal. Driven by the Initiator to select a Target and driven by a Target to Re-Select an Initiator. This signal does not have a programmable active internal pull-up. The input is Schmitt triggers input with nominal hysteresis of 400mV.                                                                                 |

| RSET#<br>(48mA)     | 158                                 | I/O<br>OC       | Reset#: The SCSI Bus Device Reset signal. This can be driven by any device to clear all devices from the bus. This signal does not have a programmable active internal pull-up. The input is Schmitt triggers input with nominal hysteresis of 400mV.                                                                                                               |

| ATN# (48mA)         | 160                                 | I/O<br>OC<br>TS | Attention#: Used by the Initiator to get the Target to respond and change the bus phase to Message Out. It has a 48mA N-channel pull-down and a programmable 4mA N-channel pull-up. The input is Schmitt triggers input with nominal hysteresis of 400mV.                                                                                                           |

| MSG#<br>(48mA)      | 153                                 | I/O<br>OC<br>TS | <b>Message Phase#:</b> Driven by the Target to indicate the Bus phase (refer to the SCSI Bus Phase Table in the SCSI Block Description). It has a 48mA N-channel pull-down and a programmable 4mA N-channel pull-up. The input is Schmitt triggers input with nominal hysteresis of 400mV.                                                                          |

| C/D#<br>(48mA)      | 150                                 | I/O<br>OC<br>TS | Command/Data#: Driven by the Target to indicate the Bus phase (refer to the SCSI Bus Phase Table in the SCSI Block Description). It has a 48mA N-channel pull-down and a programmable 4mA N-channel pull-up. The input is Schmitt triggers input with nominal hysteresis of 400mV.                                                                                  |

| I/O#<br>(48mA)      | 148                                 | I/O<br>OC<br>TS | Input/Output#: Driven by the Target to indicate the Bus phase (refer to the SCSI Bus Phase Table in the SCSI Block Description). It has a 48mA N-channel pull-down and a programmable 4mA N-channel pull-up. The input is Schmitt triggers input with nominal hysteresis of 400mV.                                                                                  |

| REQ#<br>(48mA)      | 152                                 | I/O<br>OC<br>TS | Request#: Driven by the Target to transfer data to or request data from the Initiator. It has a 48mA N-channel pull-down and a programmable 4mA N-channel pull-up. The input is Schmitt triggers input with nominal hysteresis of 400mV.                                                                                                                            |

| ACK#<br>(48mA)      | 156                                 | I/O<br>OC<br>TS | <b>Acknowledge#:</b> Driven by the Initiator to acknowledge the receipt of data or to signal the Initiator that the requested data is available. It has a 48mA N-channel pull-down and a programmable 4mA N-channel pull-up. The input is Schmitt triggers input with nominal hysteresis of 400mV.                                                                  |

| SD[15:8]#<br>(48mA) | 15,16,<br>18,19,<br>144-146,<br>149 | I/O<br>OC<br>TS | SCSI Data [15:8]#: These bidirectional active low signals are the SCSI Data signals. They have 48mA N-channel pull-downs and a programmable 4mA N-channel pull-up. The inputs are Schmitt triggers inputs with nominal hysteresis of 400mV. Logically they function the same in both single-ended and differential modes. Note: Must be deasserted when not in use. |

| SD[7:0]#<br>(48mA)  | 3-5, 7-9,<br>11, 13                 | I/O<br>OC<br>TS | SCSI Data [7:0]#: These bidirectional active low signals are the SCSI Data signals. They have 48mA N-channel pull-downs and a programmable 4mA N-channel pull-up. The inputs are Schmitt triggers inputs with nominal hysteresis of 400mV. Logically they function the same in both single-ended and differential modes.                                            |

| SDP1#<br>(48mA)     | 14                                  | I/O<br>OC<br>TS | SCSI Parity 1#: Odd parity for SCSI Data 15-8. Same buffer as the data.                                                                                                                                                                                                                                                                                             |

| SDP0#<br>(48mA)     | 1                                   | I/O<br>OC<br>TS | SCSI Parity 0#: Odd parity for SCSI Data 7-0. Same buffer as the data.                                                                                                                                                                                                                                                                                              |

## **Miscellaneous Pins**

Table 2-4. Miscellaneous Pins

| Symbol      | Pin<br>Number | VO | Function                                                                                                                                                                                                                            |

|-------------|---------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSCI        | 101           | I  | Oscillator In: This free-running or gated clock signal is used to generate timing and synchronize transfers with the BA-81C15. It also is used for internal chip timing and is divided to produce external timing for the SCSI bus. |

| EXT_ADD_ALE | 117           | 0  | External Address ALE: Active high signal to latch the ROM Data Signals through I/O or Memory Register 27h.                                                                                                                          |

## **Power/Ground Pins**

Table 2-5. Power/Ground Pins

| Symbol | Pin Number                                                                                                      | Function                     |  |

|--------|-----------------------------------------------------------------------------------------------------------------|------------------------------|--|

| VDD    | 10, 24, 35, 51, 60, 73, 86, 101, 104, 116, 129, 138, 147, 155                                                   | +5 Volt Power Pins (14 pins) |  |

| VSS    | 2, 6, 12, 17, 22, 32, 39, 47, 55, 58, 62, 71, 78, 84, 91, 97, 102, 110, 118, 125, 131, 136, 140, 143, 151, 157, | VSS—Ground Pins (26 pins)    |  |

# **Address Space**

# **About This Chapter**

Read this chapter to find out

■ A summary of the address space for BA-81C15 I/O space

# **Address Space**

The following is a summary of the address space for BA-81C15 I/O space.

| 00-3F | BUS MASTER REGISTER FILE                                        |

|-------|-----------------------------------------------------------------|

| 40-77 | SCSI REGISTER FILE                                              |

| 80-FF | SCATTER/GATHER INSTRUCTION RAM ADDRESSABLE AS DOUBLE WORDS ONLY |

| 80-FF | SHADOWED SCSI AUTOMATION HAM ADDRESSABLE AS BYTES OR WORD ONLY  |

**Note:** Shadowed area is only addressable if the shadow bit is set in the Feature Control Register 29h Bit 1.

## **Register Reset Condition Description**

## **About This Chapter**

Read this chapter to find out

- PCI Configuration Space Register reset conditions

- Host Register File reset conditions

- Block Register reset conditions

# **Register Reset Condition Description**

# **PCI Configuration Space Register Reset Condition**

| REGISTER<br>NUMBER | POWER ON<br>RESET | CHIP RESET | DRIVER RESET                           | REGISTER VALUE<br>7 6 5 4 3 2 1 0 |

|--------------------|-------------------|------------|----------------------------------------|-----------------------------------|

| 00                 |                   |            |                                        | 01001011                          |

| 01                 |                   |            |                                        | 00010000                          |

| 02                 |                   |            |                                        | 00110000                          |

| 03                 |                   |            |                                        | 1000001                           |

| 04                 | *                 | *          |                                        | 1000000                           |

| 05                 | *                 | *          |                                        | 0000000                           |

| 06                 | *                 | *          |                                        | 0000000                           |

| 07                 | *                 | *          |                                        | 0000000                           |

| 08                 | *                 | *          |                                        | 0000010                           |

| 09                 | *                 | *          |                                        | 0000000                           |

| 0A                 | *                 | *          |                                        | 0000000                           |

| 0B                 | *                 | *          |                                        | 00000001                          |

| 0C                 | *                 | *          |                                        | 0000000                           |

| 0D                 | *                 | *          | 1000                                   | 0000000                           |

| 0E                 | *                 | *          |                                        | 0000000                           |

| 0F                 | *                 | *          |                                        | 0000000                           |

| 10                 | *                 | *          |                                        | 00000001                          |

| 11                 | *                 | *          |                                        | 0000000                           |

| 12                 | *                 | *          |                                        | 0000000                           |

| 13                 | *                 | *          |                                        | 0000000                           |

| 14                 | *                 | *          |                                        | 0000000                           |

| 15                 | *                 | *          |                                        | 0000000                           |

| 16                 | *                 | *          |                                        | 0000000                           |

| 17                 | *                 | *          | *                                      | 0000000                           |

| 18                 | *                 | *          |                                        | 0000000                           |

| 19                 | *                 | *          |                                        | 0000000                           |

| 1A                 | *                 | *          | ************************************** | 0000000                           |

| 1B                 | *                 | *          | *                                      | 0000000                           |

| REGISTER<br>NUMBER | POWER ON<br>RESET | CHIP RESET                             | DRIVER RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | REGISTER VALUE<br>7 6 5 4 3 2 1 0 |

|--------------------|-------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 1C                 |                   |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0000000                           |

| 1D                 |                   |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00000000                          |

| 1E                 |                   |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0000000                           |

| 1F                 |                   |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00000000                          |

| 20                 |                   |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0000000                           |

| 21                 | *                 | *                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0000000                           |

| 22                 | *                 | *                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0000000                           |